CDCVF2510APW

CDCVF2510APW

- 描述

- CDCVF2510A 具有断电模式的 3.3V 锁相环路时钟驱动器

- 品牌名称

- TI(德州仪器)

- 商品型号

- CDCVF2510APW

- 商品编号

- C524258

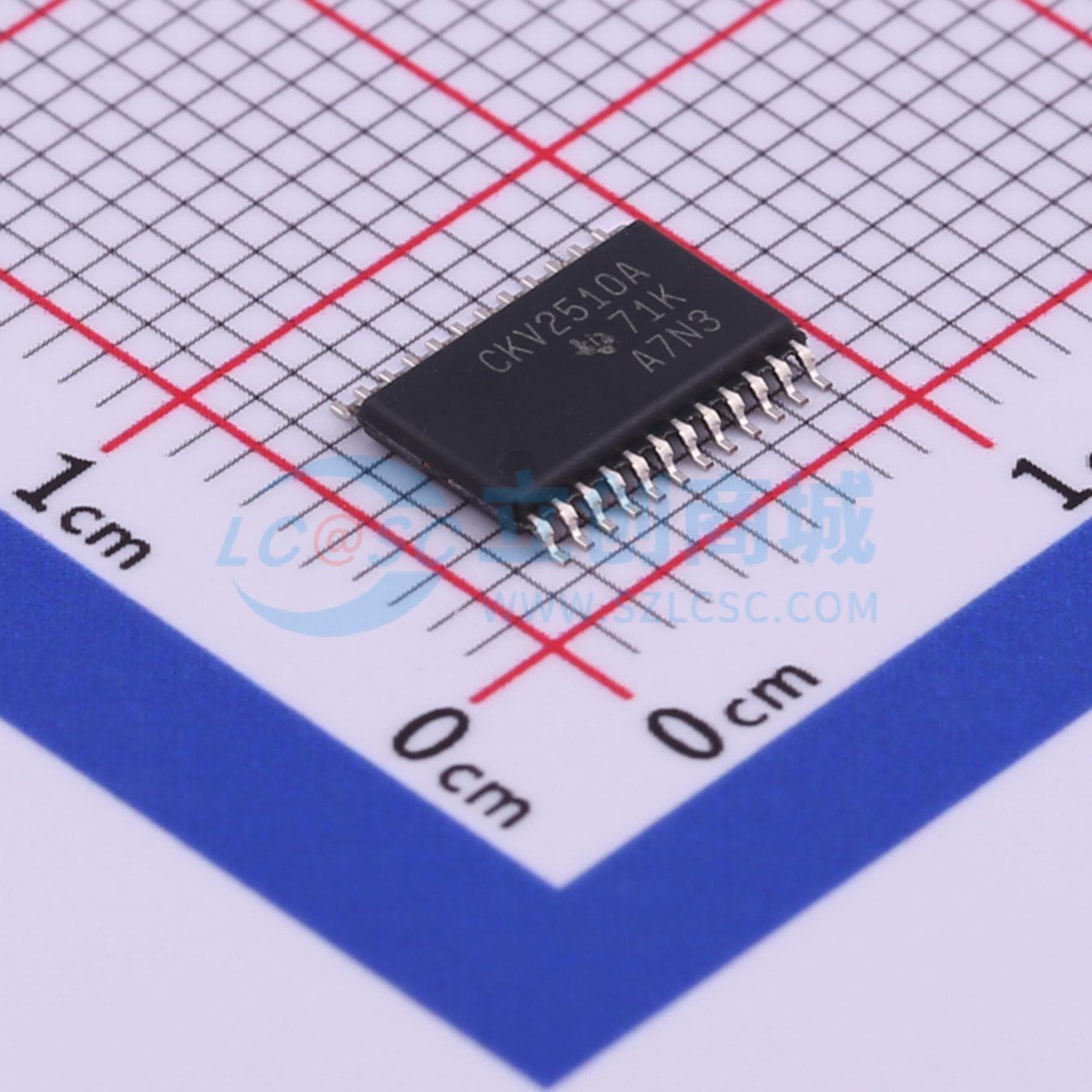

- 商品封装

- TSSOP-24

- 包装方式

- 管装

- 商品毛重

- 0.08克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 时钟缓冲器/驱动器/分配器 | |

| 最大输出频率 | 175MHz | |

| 输入通道数 | 1 | |

| 输出通道数 | 10 |

| 属性 | 参数值 | |

|---|---|---|

| 工作电压 | 3V~3.6V | |

| 输出偏斜 | - | |

| 工作温度 | 0℃~+85℃ | |

| 功能特性 | 内置锁相环;输出使能/关断 |

商品概述

CDCVF2510A是一款高性能、低偏斜、低抖动的锁相环(PLL)时钟驱动器。CDCVF2510A使用锁相环(PLL)在频率和相位上精确对齐反馈(FBOUT)输出与时钟(CLK)输入信号。它专为同步DRAM设计。CDCVF2510A在3.3V VCC下工作,还提供集成的串联阻尼电阻,非常适合驱动点对点负载。 一组10个输出提供10个低偏斜、低抖动的CLK副本。输出信号占空比被调整为50%,与CLK处的占空比无关。输出通过控制(G)输入进行使能或禁用。当G输入为高电平时,输出与CLK在相位和频率上同步切换;当G输入为低电平时,输出被禁用并处于逻辑低电平状态。当CLK没有输入信号(<1 MHz)时,器件自动进入掉电模式;输出变为低电平状态。 与许多包含PLL的产品不同,CDCVF2510A不需要外部RC网络。PLL的环路滤波器集成在芯片上,最大限度地减少了元件数量、电路板空间和成本。 由于基于PLL电路,CDCVF2510A需要一段稳定时间来实现反馈信号与参考信号的锁相。在上电、CLK施加固定频率和固定相位信号之后,或者PLL参考或反馈信号发生任何变化之后,都需要这段稳定时间。通过将AVCC接地,可以绕过PLL,将其用作简单的时钟缓冲器。 CDCVF2510A的工作温度范围为0℃至85℃。

商品特性

- 设计满足并超越PC133 SDRAM注册DIMM规范修订版1.1

- 支持扩频时钟

- 工作频率为20 MHz至175 MHz

- 在66 MHz至166 MHz时,静态相位误差分布为±125 ps

- 在66 MHz至166 MHz时,抖动(周期-周期)为|70| ps

- 先进的深亚微米工艺使功耗比当前一代PC133器件降低40%以上

- 自动频率检测以禁用器件(掉电模式)

- 采用塑料24引脚TSSOP封装

- 将一个时钟输入分配到一组10个输出

- 外部反馈(FBIN)端子用于使输出与时钟输入同步

- 片上集成25Ω串联阻尼电阻

- 无需外部RC网络

- 在3.3V下工作

应用领域

- DRAM应用

- 基于PLL的时钟分配器

- 非PLL时钟缓冲器

相似推荐

其他推荐