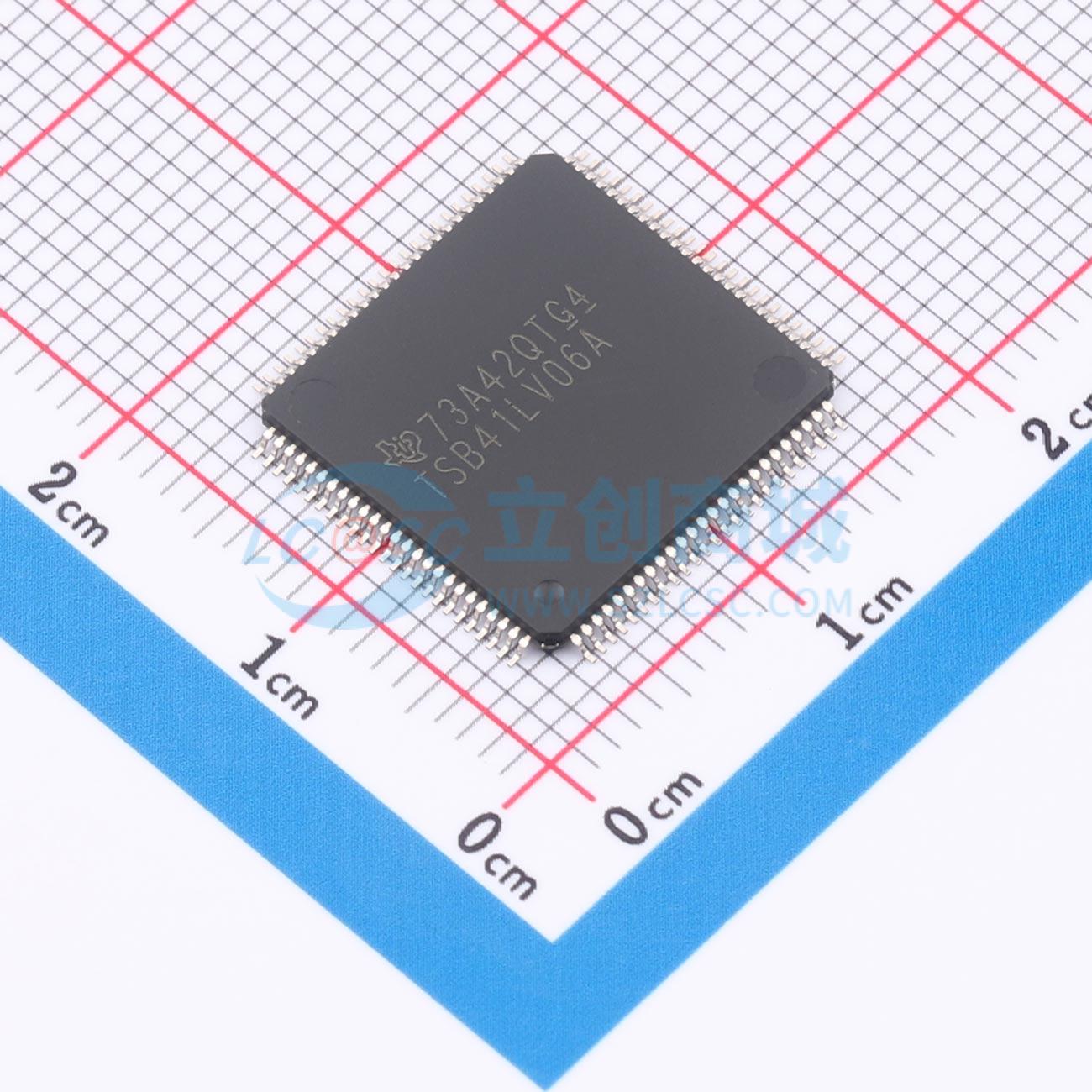

TSB41LV06APZP

IEEE 1394a 六端口电缆收发器/仲裁器

- 描述

- 该芯片提供数字和模拟收发器功能,以实现基于电缆的 IEEE 1394 网络中的六端口节点。每个电缆端口包含两个差分线收发器。

- 品牌名称

- TI(德州仪器)

- 商品型号

- TSB41LV06APZP

- 商品编号

- C1544415

- 商品封装

- HTQFP-100(14x14)

- 包装方式

- 托盘

- 商品毛重

- 0.001克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 其他接口 | |

| 接口类型 | - | |

| 数据速率 | 400Mbps | |

| 工作电压 | 3V~3.6V |

| 属性 | 参数值 | |

|---|---|---|

| 工作温度 | 0℃~+70℃ | |

| 工作电流 | 280mA;204mA;164mA | |

| 静态电流 | 150uA | |

| 功能特性 | 唤醒功能;接口自动省电;使能/关断功能 |

商品概述

TSB41LV06A提供了在基于电缆的IEEE 1394网络中实现六端口节点所需的数字和模拟收发器功能。每个电缆端口包含两个差分线路收发器。这些收发器包括用于监测线路状况的电路,以确定连接状态、进行初始化和仲裁,以及进行数据包的接收和传输。TSB41LV06A设计用于与链路层控制器(LLC)接口,如TSB12LV21、TSB12LV22、TSB12LV23、TSB12LV31、TSB12LV41、TSB12LV42或TSB12LV01A。 TSB41LV06A仅需一个外部24.576 MHz晶体作为参考。也可以提供外部时钟代替晶体。内部振荡器驱动内部锁相环(PLL),该锁相环产生所需的393.216 MHz参考信号。该参考信号在内部进行分频,以提供用于控制输出编码选通和数据信息传输的时钟信号。一个49.152 MHz的时钟信号被提供给相关的LLC,用于两个芯片的同步,并用于对接收到的数据进行重新同步。当通过将PD端子置高来启用掉电(PD)功能时,PLL停止工作。 TSB41LV06A支持在其自身与LLC之间设置可选的隔离屏障。当ISO输入端子接高电平时,LLC接口输出正常工作。当ISO端子接低电平时,内部差分逻辑被启用,输出驱动方式使得它们可以通过电容或变压器电隔离屏障进行耦合,如IEEE Std 1394 - 1995附录J和P1394a补充文件(第5.9.4节)中所述(以下称为附录J型隔离)。要使用TI总线保持器隔离,PHY上的ISO端子必须为高电平。 要通过电缆端口传输的数据位从LLC通过两条、四条或八条并行路径(取决于请求的传输速度)接收,并在TSB41LV06A内部与49.152 MHz系统时钟同步锁存。这些位被串行组合、编码,并以98.304、196.608或393.216 Mbit/s(分别称为S100、S200和S400速度)作为输出数据选通信息流进行传输。在传输过程中,编码后的数据信息在TPB电缆对上进行差分传输,编码后的选通信息在TPA电缆对上进行差分传输。 在数据包接收期间,接收电缆端口的TPA和TPB发送器被禁用,该端口的接收器被启用。编码后的数据信息在TPA电缆对上接收,编码后的选通信息在TPB电缆对上接收。接收到的数据选通信息被解码,以恢复接收时钟信号和串行数据位。串行数据位被拆分为两条、四条或八条位的并行流(取决于指示的接收速度),与本地49.152 MHz系统时钟重新同步,并发送到相关的LLC。接收到的数据也会在其他活动(已连接)的电缆端口上传输(转发)。 TPA和TPB电缆接口都包含差分比较器,用于在初始化和仲裁期间监测线路状态。这些比较器的输出被内部逻辑用于确定仲裁状态。TPA通道监测输入电缆的共模电压。该共模电压的值在仲裁期间用于设置下一个数据包传输的速度。此外,TPB通道监测TPB对上输入电缆的共模电压,以检测是否存在远程提供的双绞线偏置电压。 TSB41LV06A在TPBIAS端子处为端口端接提供1.86 V的标称偏置电压。PHY包含六个独立的TPBIAS电路。

商品特性

- 完全支持IEEE 1394−1995高性能串行总线标准及P1394a补充文件的规定

- 与IEEE Std 1394的FireWire和i.LINK实现完全互操作

- 完全符合OpenHCI要求

- 提供六个符合P1394a标准的电缆端口,传输速率为100/200/400 Mbit/s

- 全面的P1394a支持包括:连接去抖、仲裁短复位、多速级联、仲裁加速、飞越级联、端口禁用/挂起/恢复

- 扩展恢复信号,以与旧版DV设备兼容

- 电池供电应用中的节能掉电特性包括:挂起期间自动设备掉电、设备掉电端子、通过LPS禁用链路接口以及停用端口掉电

- 超低功耗睡眠模式

- 节点功率类别信息信号,用于系统电源管理

- 电缆电源存在监测

- 电缆端口监测线路状况,以确定与远程节点的活动连接

- 寄存器位允许软件控制竞争位、功率类别位、链路活动控制位和P1394a特性

- 通过2/4/8条并行线以49.152 MHz的频率与链路层控制器进行数据接口

- 与链路层控制器的接口支持低成本TI总线保持器隔离和可选的附录J电气隔离

- 可与使用3.3 V和5 V电源的链路层控制器互操作

- 可与使用3.3 V和5 V电源的其他物理层(PHY)互操作

- 低成本24.576 MHz晶体提供100/200/400 Mbit/s的发送和接收数据,以及49.152 MHz的链路层控制器时钟

- 输入数据与本地时钟重新同步

- 逻辑执行系统初始化和仲裁功能

- 包含数据选通位级编码的编码和解码功能

- 每个端口有独立的电缆偏置(TPBIAS)

- 单3.3 V电源供电

- 低成本高性能100引脚TQFP(PZP)热增强封装

- 可直接替代升级TSB41LV06PZP