NB6L295MNG

双沟道可编程延迟线路,带 LVPECL 输出

SMT扩展库PCB免费打样

私有库下单最高享92折

- 描述

- NB6L295 是一款双沟道可编程延迟芯片,主要适用于时钟或数据去摆和计时调节. NB6L295 功能多样,两个单独的可变延迟沟道 PD0 和 PD1 可配置为两种运行模式之一,双延迟或扩展延迟。在双延迟模式下,每个沟道均具有一个可编程延迟部分,设计为使用门极矩阵和多路复用器链条。每个沟道具有固定最小延迟 3.2 ns。扩展延迟模式相当于 PD0 和 PD1 的相加延迟,并且通过将串行数据接口 MSEL 位设置为高电平来实现。这样会将 PD0 输出内部级联到 PD1 的输入中。因此,扩展延迟路径在 IN0/IN0 输入处开始,流经 PD0,级联到 PD1,然后通过 Q1/Q1 输出。扩展延迟模式具有固定最小延迟 6 ns。通过 3 引脚串行数据接口对每个延迟沟道进行编程可以实现所需延迟,如应用部分描述的那样。这种可数字选择延迟的增量分辨率通常为 11 ps,双延迟模式下的净可编程延迟范围为每沟道 0 ns 至 6 ns;扩展延迟模式为 0 ns 至 11.2 ns。多电平输入可通过差分 LVPECL、LVDS 或 CML 逻辑电平;或单端 LVPECL、LVCMOS 或 LVTTL 直接驱动。一个启用引脚可用于控制两个输入。SDI 输入引脚由 LVCMOS 或 LVTTL 电平信号控制。NB6L295 LVPECL 输出包含温度补偿电路。此器件采用 4 mm x 4 mm 24 引脚 QFN 无铅封装。NB6L295 属于一款 ECLinPS MAX 系列高性能产品。

- 品牌名称

- onsemi(安森美)

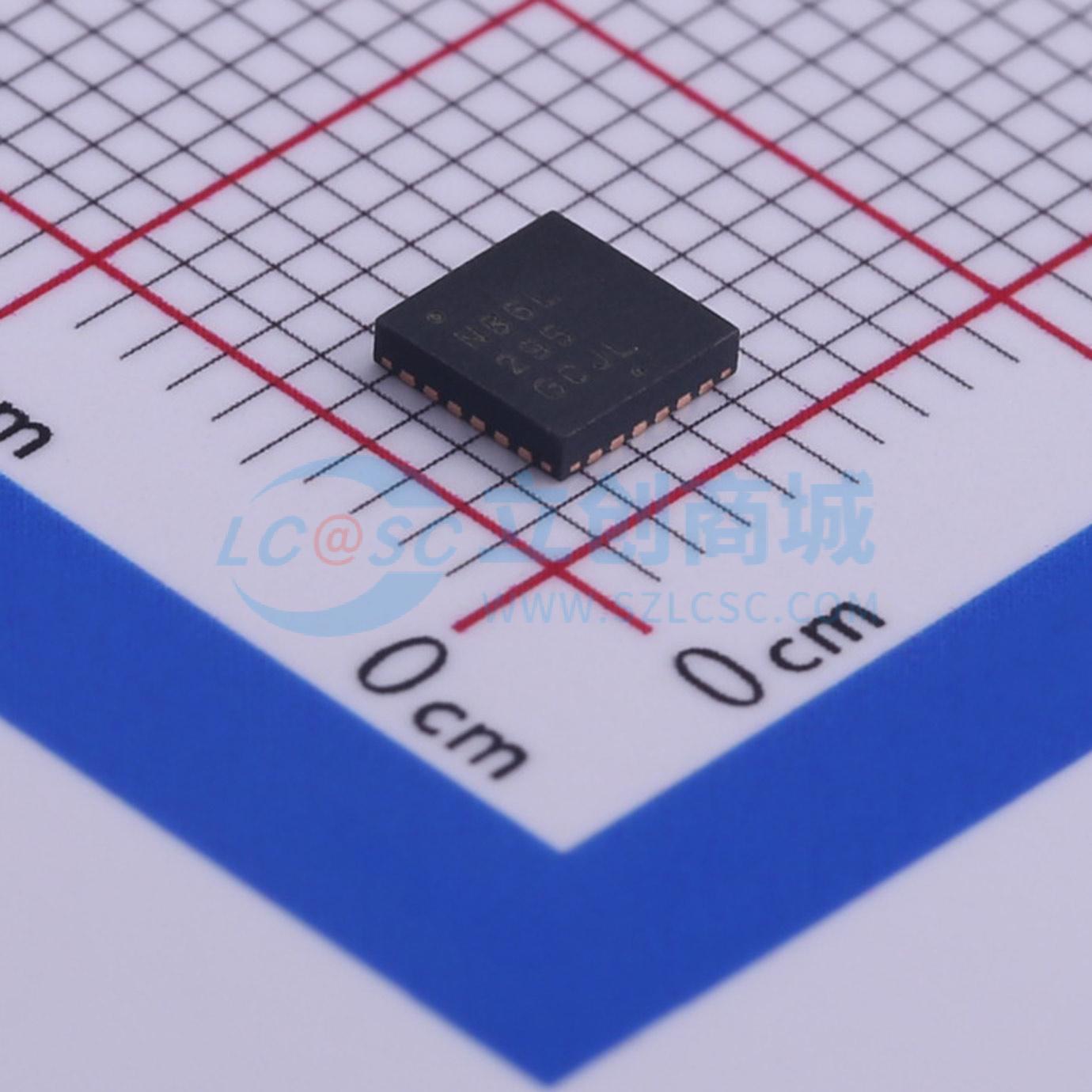

- 商品型号

- NB6L295MNG

- 商品编号

- C464032

- 商品封装

- QFN-24-EP(4x4)

- 包装方式

- 管装

- 商品毛重

- 0.077克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 时钟延迟 | |

| 可用总延迟范围 | 6ns~17ns | |

| 工作电压 | 2.375V~3.6V |

| 属性 | 参数值 | |

|---|---|---|

| 输出电平 | LVPECL | |

| 工作温度 | -40℃~+85℃ | |

| 功能特性 | 数字配置接口;可编程时钟延迟;细粒度延迟步进 |

商品概述

NB6L295是一款双通道可编程延迟芯片,主要用于时钟或数据去偏斜和时序调整。NB6L295功能多样,两个独立的可变延迟通道PD0和PD1可配置为两种工作模式之一:双延迟模式或扩展延迟模式。 在双延迟模式下,每个通道都有一个可编程延迟部分,该部分采用门矩阵和多路复用器链设计。每个通道的固定最小延迟为3.2 ns。 扩展延迟模式相当于PD0和PD1的延迟相加,通过将串行数据接口MSEL位设置为高电平来实现。这将在内部把PD0的输出级联到PD1的输入。因此,扩展延迟路径从IN0/IN0输入开始,经过PD0,级联到PD1,然后通过Q1/Q1输出。扩展延迟模式的固定最小延迟为6 ns。 所需的延迟通过一个3引脚串行数据接口对每个延迟通道进行编程来实现,具体编程方法在应用部分介绍。数字可选延迟的增量分辨率通常为11 ps,在双延迟模式下,每个通道的净可编程延迟范围为0 ns至6 ns;在扩展延迟模式下,为0 ns至11.2 ns。 多级输入可由差分LVPECL、LVDS或CML逻辑电平直接驱动;也可由单端LVPECL、LVCMOS或LVTTL驱动。有一个单独的使能引脚可用于控制两个输入。SDI输入引脚由LVCMOS或LVTTL电平信号控制。NB6L295的LVPECL输出包含温度补偿电路。该器件采用4 mm x 4 mm 24引脚QFN无铅封装。

商品特性

- 输入时钟频率>1.5 GHz,输出峰峰值电压为550 mV

- 输入数据速率>2.5 Gb/s

- 可编程延迟范围:每个延迟通道0 ns至6 ns

- 可编程延迟范围:扩展延迟模式下0 ns至11.2 ns

- 总延迟范围:每个延迟通道3.2 ns至8.8 ns

- 总延迟范围:扩展延迟模式下6 ns至17 ns

- 单调延迟:以11 ps为增量,共511步

- 线性度:最大±20 ps

- 典型上升和下降时间:100 ps

- 典型时钟抖动:均方根值为3 ps

- 典型数据相关抖动:峰峰值为20 ps

- 与LVPECL、CML或LVDS差分输入兼容

- 与LVPECL、LVCMOS、LVTTL单端输入兼容

- 三线串行接口

- 输入使能/禁用

- 工作范围:VCC = 2.375 V至3.6 V

- 典型LVPECL输出电平:峰峰值为780 mV

- 提供内部50 Ω输入端接

- 环境工作温度:-40℃至85℃

- 24引脚QFN封装,4 mm x 4 mm

- 这些器件为无铅器件