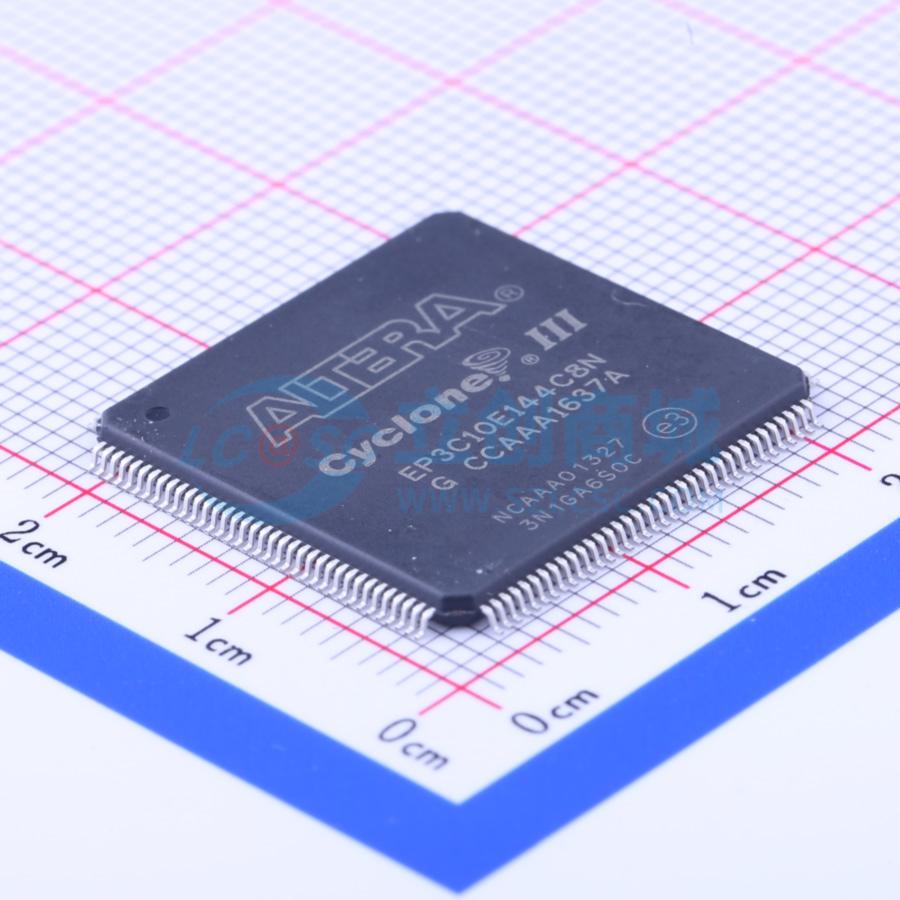

EP3C10E144C8N

EP3C10E144C8N

SMT扩展库PCB免费打样

私有库下单最高享92折

- 品牌名称

- Intel/Altera

- 商品型号

- EP3C10E144C8N

- 商品编号

- C39855

- 商品封装

- PQFP-144-EP(20x20)

- 包装方式

- 托盘

- 商品毛重

- 8克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 可编程逻辑器件(CPLD/FPGA) | |

| 类型 | - | |

| 工作电压(VCCIO) | - | |

| 逻辑单元数 | 10320 |

| 属性 | 参数值 | |

|---|---|---|

| 逻辑阵列块数量 | 645 | |

| 内嵌式块RAM(eRAM) | 423936bit | |

| 工作温度 | 0℃~+85℃ | |

| 功能特性 | 支持SEU检错纠错;支持多版本位流回退功能;支持热插拔;支持AES加密 |

商品概述

Cyclone III 器件系列提供了一种独特的组合,集高功能、低功耗和低成本于一体。基于台湾半导体制造公司(TSMC)的低功耗(LP)工艺技术、硅优化以及软件特性来最小化功耗,Cyclone III 器件系列为大批量、低功耗且成本敏感的应用提供了理想的解决方案。为了满足独特的设计需求,Cyclone III 器件系列提供了两种变体:

- Cyclone III:最低功耗,高功能,且成本最低。

- Cyclone III LS:具有安全特性的最低功耗FPGA。

该系列器件逻辑元件(LEs)密度范围从大约5,000到200,000,内存容量从0.5兆位(Mb)到8 Mb不等,静态功耗低于1%瓦,使得更容易达到功率预算。Cyclone III LS 器件是首个在低功耗和高功能性FPGA平台上实现一系列安全特性的产品,这些安全特性保护IP免受篡改、逆向工程和克隆。此外,Cyclone III LS 器件支持设计分离,这允许在单个芯片中引入冗余以减少应用的尺寸、重量和功耗。

Cyclone III 器件系列的关键特性包括:

-

最低功耗FPGA:

- 采用TSMC低功耗工艺技术和Altera 功率感知设计流程,实现最低功耗。

- 低功耗运行延长了便携式和手持设备的电池寿命,减少了或消除了冷却系统的成本,并支持在热挑战环境中操作。

- 支持热插拔操作。

-

设计安全特性:

- 使用256位易失性密钥的高级加密标准(AES)进行配置安全。

- Quartus II 软件优化的路由架构,适用于设计分离流程。

- 设计分离流程实现了设计分区之间的物理和功能隔离。

- 可禁用外部JTAG端口。

- 错误检测(ED)周期指示器提供每个ED周期的通过或失败指示,并对配置随机访问存储器(CRAM)位的有意或无意更改提供可见性。

- 能够执行清零操作以清除FPGA逻辑、CRAM、嵌入式存储器和AES密钥的内容。

- 内部振荡器启用系统监控和健康检查功能。

-

增强系统集成:

- 高内存与逻辑比及乘法器与逻辑比。

- 高I/O数,适用于用户I/O受限应用的低至中密度器件。

- 可调节I/O转换速率以改善信号完整性。

- 支持LVTTL、LVCMOS、SSTL、HSTL、PCI、PCI-X、LVPECL、总线LVDS(BLVDS)、LVDS、mini-LVDS、RSDS和PPDS等I/O标准。

- 支持多值片上端接(OCT)校准功能,以消除过程、电压和温度(PVT)变化的影响。

- 每个器件四个锁相环(PLL),为器件时钟管理、外部系统时钟管理和I/O接口提供强大的时钟管理和合成能力。

- 每个PLL五个输出,可级联以节省I/O,简化PCB布线并减少抖动。

- 无需外部控制器即可远程升级系统。

- 专用循环冗余校验电路用于检测单事件翻转(SEU)问题。

- Nios II 嵌入式处理器为Cyclone III器件系列提供低成本和定制化的嵌入式处理解决方案。

- Altera及其合作伙伴计划(AMPP)提供的大量预构建和验证过的IP内核。

- 支持高速外部存储器接口,如DDR、DDR2、SDR SDRAM和QDRII SRAM。

- 自动校准PHY功能简化了定时闭合过程,并消除了DDR、DDR2和QDRII SRAM接口的PVT变化影响。

- 垂直迁移允许在给定封装下跨器件密度迁移到其他具有相同专用引脚、配置引脚和电源引脚的器件,从而随着设计的发展优化器件密度和成本。