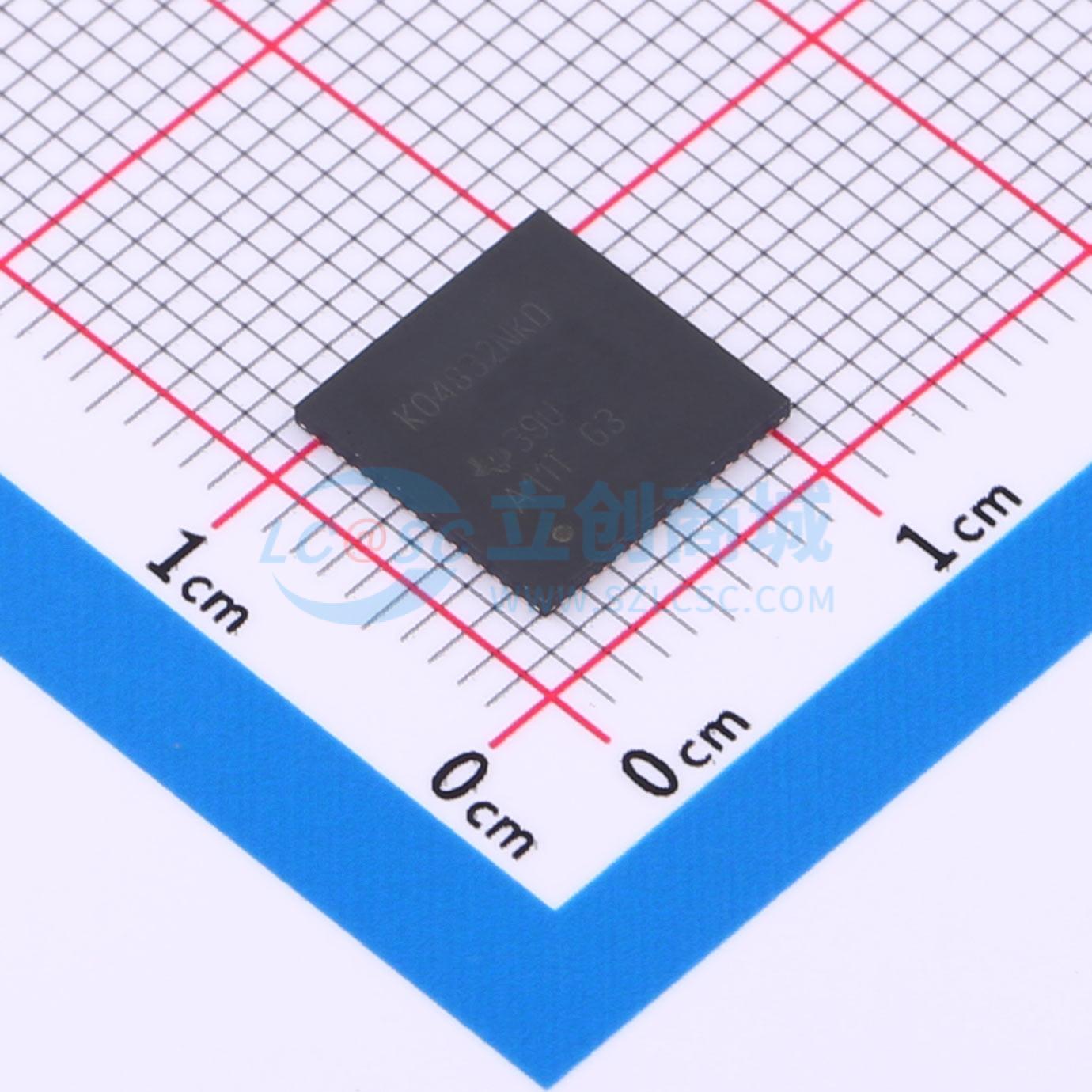

LMK04832NKDT

带双环路PLL且符合JESD204B标准的超低噪声时钟抖动清除器

SMT扩展库PCB免费打样

私有库下单最高享92折

- 描述

- LMK04832 具有双环路且符合 JESD204B 标准的超低噪声 3.2GHz、15 路输出时钟抖动清除器

- 品牌名称

- TI(德州仪器)

- 商品型号

- LMK04832NKDT

- 商品编号

- C2868953

- 商品封装

- WQFN-64(9x9)

- 包装方式

- 编带

- 商品毛重

- 0.353333克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 时钟发生器/频率合成器/PLL | |

| 接口类型 | SPI | |

| 最大输出频率 | 3255MHz | |

| 工作电压 | 3.15V~3.45V | |

| 输出通道数 | 14 | |

| 工作温度 | -40℃~+85℃ | |

| 周期抖动 | - |

| 属性 | 参数值 | |

|---|---|---|

| 相邻周期抖动 | - | |

| 相位抖动 | 54fs;61fs;64fs;67fs | |

| 相位偏移 | 支持 | |

| 时钟/振荡器 | 外置 | |

| 输入电平 | - | |

| 输出电平 | LVPECL;LVCMOS;LVDS;CML | |

| 功能特性 | - |

商品概述

LMK04832 是一款具有超高性能的时钟调节器,不但支持JEDEC JESD204B,而且与LMK0482x 器件系列引脚兼容。 PLL2 可以配置14 个时钟输出以驱动7 个JESD204B 转换器或其他逻辑器件(使用器件和SYSREF 时钟)。SYSREF 可以通过直流和交流耦合提供。不只是JESD204B 应用,14 个输出中的每一个输出都可以单独配置为用于传统时钟系统的高性能输出。 LMK04832 可以配置在双PLL、单PLL 或时钟分配模式下工作(使用或不使用SYSREF 生成或时钟恢复)。PLL2 可以使用内部或外部VCO 工作。 LMK04832 既具有出色的性能,又具有多种特性,如功率和性能均衡调节、双VCO、动态数字延迟和保持模式,是提供灵活的高性能时钟树的理想器件。

商品特性

- 最高时钟输出频率:3255MHz

- 多模式:双PLL、单PLL 和时钟分配

- 超低噪声,2500MHz 时:

- 54fs RMS 抖动(12kHz 至20MHz)

- 64fs RMS 抖动(100Hz 至20MHz)

- –157.6dBc/Hz 本底噪声

- 超低噪声,3200MHz 时:

- 61fs RMS 抖动(12kHz 至20MHz)

- 67fs RMS 抖动(100Hz 至100MHz)

- –156.5dBc/Hz 本底噪声

- PLL2:

- –230dBc/Hz PLL FOM

- –128dBc/Hz PLL 1/f

- 相位检测器速率高达320MHz

- 两个集成VCO:2440 至2580MHz 和2945 至3255MHz

- 多达14 个差动器件时钟CML、LVPECL、LCPECL、HSDS、LVDS 和2xLVCMOS 可编程输出

- 最多1 个缓冲VCXO/XO 输出– LVPECL、LVDS、2xLVCMOS 可编程输出

- 1 - 1023 CLKout 分频器

- 1 - 8191 SYSREF 分频器

- SYSREF 时钟25ps 阶跃模拟延迟

- 器件时钟和SYSREF 数字延迟和动态数字延迟

- PLL1 保持模式

- PLL1 或PLL2 零延迟支持

- 105°C PCB 温度(在散热焊盘上测量)

应用领域

- 测试和测量

- 雷达

- 微波回程

- 数据转换器时钟