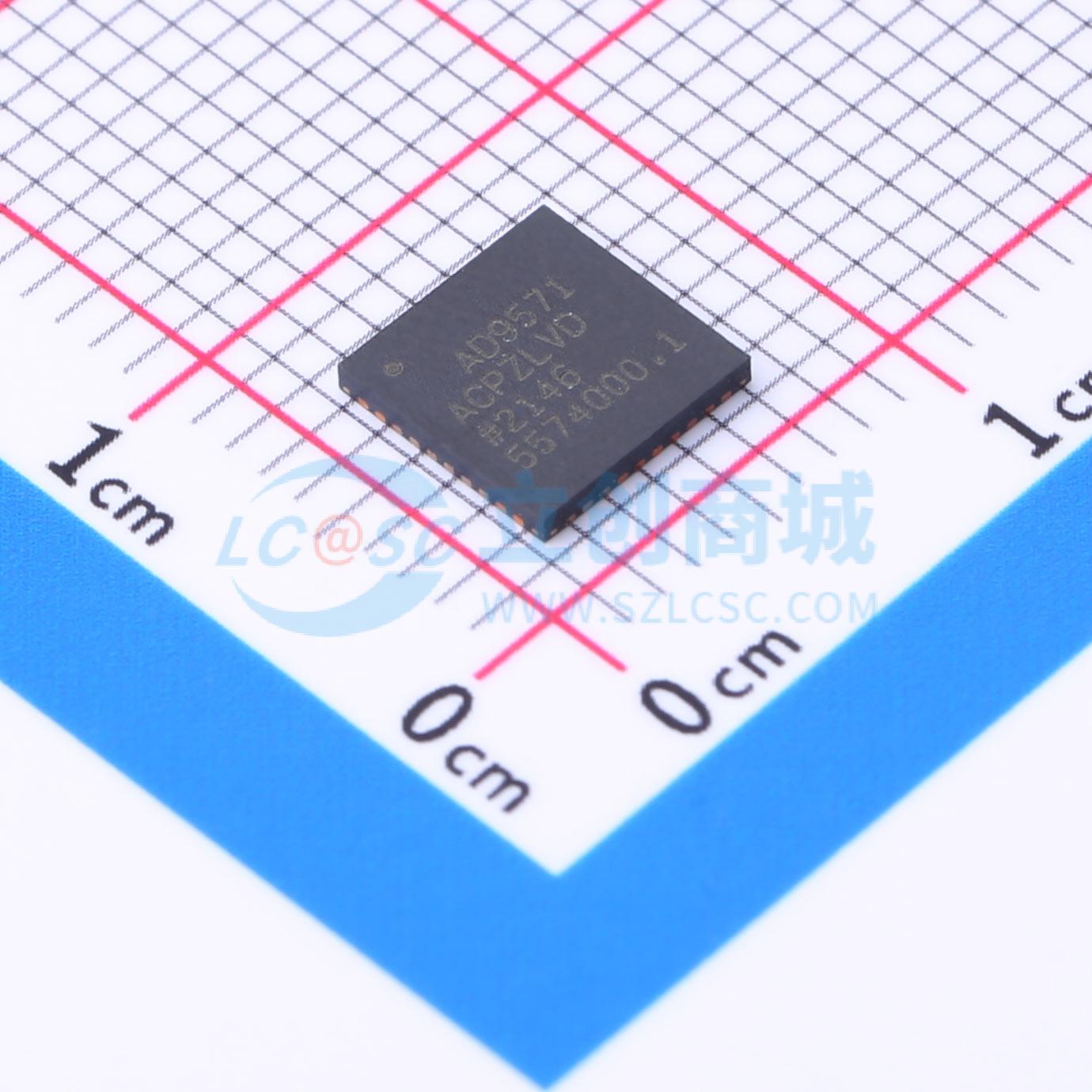

AD9571ACPZLVD

以太网时钟发生器带有10个时钟输出

SMT扩展库PCB免费打样

私有库下单最高享92折

- 描述

- 以太网时钟发生器,10路时钟输出

- 品牌名称

- ADI(亚德诺)

- 商品型号

- AD9571ACPZLVD

- 商品编号

- C653582

- 商品封装

- LFCSP-40(6x6)

- 包装方式

- 托盘

- 商品毛重

- 0.096克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 时钟发生器/频率合成器/PLL | |

| 接口类型 | - | |

| 最大输出频率 | 156.25MHz | |

| 工作电压 | 3V~3.6V | |

| 输出通道数 | 10 | |

| 工作温度 | -40℃~+85℃ | |

| 周期抖动 | - |

| 属性 | 参数值 | |

|---|---|---|

| 相邻周期抖动 | - | |

| 相位抖动 | - | |

| 相位偏移 | - | |

| 时钟/振荡器 | 内置;外置 | |

| 输入电平 | CMOS | |

| 输出电平 | CMOS;LVDS;LVPECL | |

| 功能特性 | - |

商品概述

AD9571 提供多输出时钟发生器功能,包含一个专为以太网线路卡应用优化的专用 PLL 内核。该整数 N 型 PLL 设计基于一系列经过验证的高性能、低抖动频率合成器,可最大限度提升网络性能。对相位噪声和抖动要求苛刻的其他应用也能从该器件中受益。 PLL 部分由低噪声相位 - 频率检测器 (PFD)、精密电荷泵 (CP)、低相位噪声压控振荡器 (VCO) 以及预编程的反馈分频器和输出分频器组成。通过将外部晶体或参考时钟连接到 REFCLK 引脚,最高 156.25 MHz 的频率可锁定到输入参考信号。 每个输出分频器和反馈分频器的分频比都针对所需的输出速率进行了预编程。无需外部环路滤波器组件,从而节省了宝贵的设计时间和电路板空间。 AD9571 采用 40 引脚 6 mm×6 mm 引脚框架芯片级封装,可由单一 3.3 V 电源供电。工作温度范围为 -40℃ 至 +85℃。

商品特性

- 完全集成的 VCO/PLL 内核

- 在 156.25 MHz 时,1.875 MHz 至 20 MHz 频段的均方根抖动为 0.17 ps

- 在 125 MHz 时,12 kHz 至 20 MHz 频段的均方根抖动为 0.41 ps

- 输入晶体或时钟频率为 25 MHz

- 预设 156.25 MHz、33.33 MHz、100 MHz 和 125 MHz 的分频比

- 可选 LVPECL 或 LVDS 输出格式

- 集成环路滤波器

- 6 路参考时钟输出

- 通过跳线引脚配置速率

- 节省空间的 6 mm×6 mm 40 引脚 LFCSP 封装

- 功耗 0.48 W(LVDS 工作模式)

- 功耗 0.69 W(LVPECL 工作模式)

- 3.3 V 供电

应用领域

- 以太网线路卡、交换机和路由器

- SCSI、SATA 和 PCI - Express

- 支持 PCI

- 低抖动、低相位噪声时钟生成

相似推荐

其他推荐