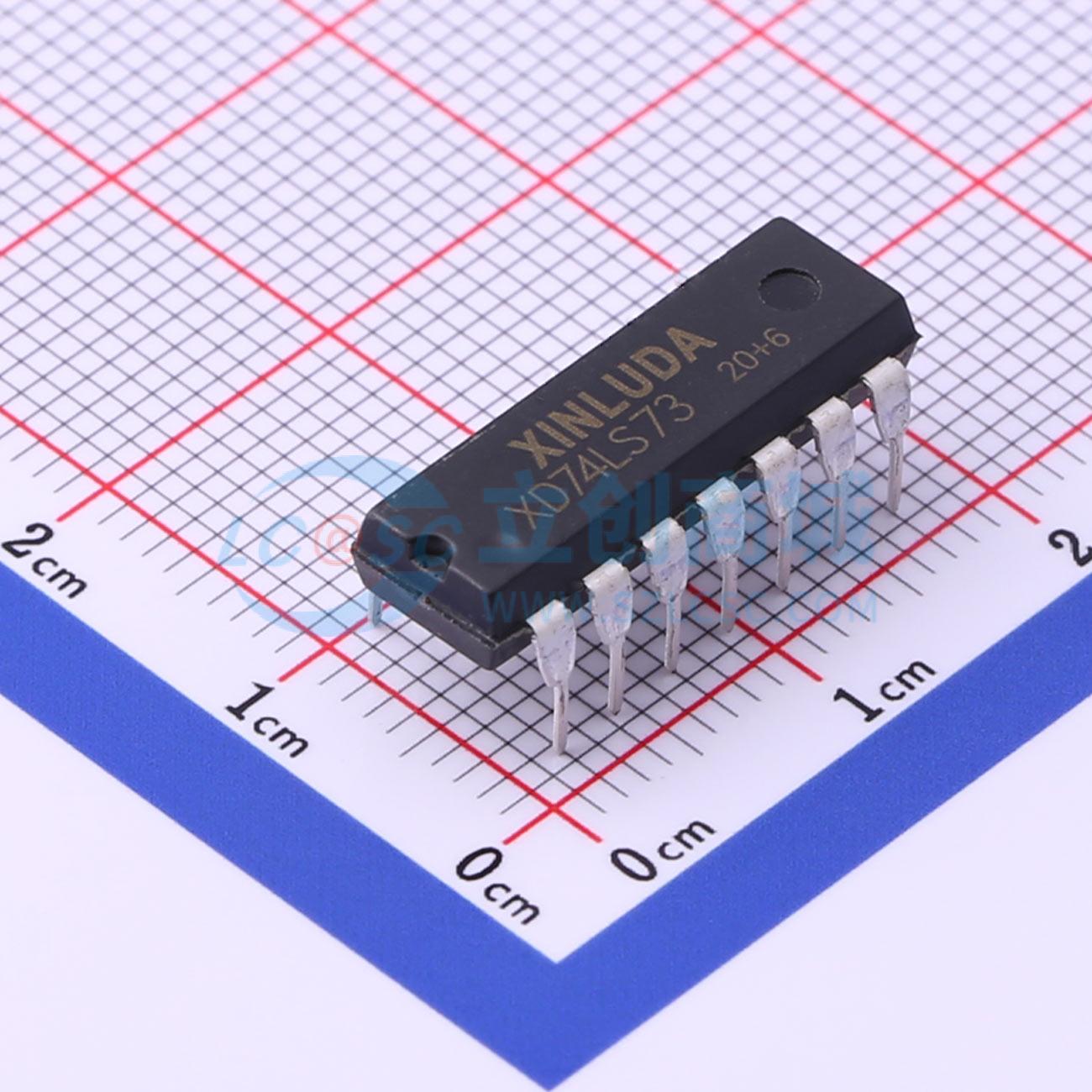

XD74LS73

双J-K触发器带清零功能

SMT扩展库PCB免费打样

私有库下单最高享92折

- 描述

- 逻辑电路 触发器 XD74LS73 包含两个独立的负沿触发器。为了实现可预测的操作,J 和 K 输入必须在时钟由高到低转换之前一个建立时间保持稳定。当清零引脚为低电平时,它会覆盖时钟和数据输入,强制 Q 输出为低电平,Q 输出为高电平。

- 品牌名称

- XINLUDA(信路达)

- 商品型号

- XD74LS73

- 商品编号

- C609760

- 商品封装

- DIP-14

- 包装方式

- 管装

- 商品毛重

- 1.674克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 触发器 | |

| 类型 | JK-型 | |

| 触发沿 | 下降沿 | |

| 工作电压 | 4.75V~5.25V | |

| 时钟频率(fc) | 8MHz | |

| 功能 | 复位 | |

| 元件数 | 2 | |

| 每个元件位数 | 1 | |

| 输出类型 | - |

| 属性 | 参数值 | |

|---|---|---|

| 传播延迟(tpd) | 20ns@5V,15pF | |

| 系列 | 74LS系列 | |

| 灌电流(IOL) | 400uA | |

| 拉电流(IOH) | 800uA | |

| 输入电容 | 15pF | |

| 工作温度 | 0℃~+70℃ | |

| 同步/异步 | 异步 | |

| 建立时间 | 20ns | |

| 保持时间 | - |

商品概述

The XD74LS73 contains two independent negative-edge-triggered flip-flops. The J and K inputs must be stable one setup time prior to the high-tolow clock transition for predictable operation.When the clear is low, 一 it overrides the clock and data inputs forcing the Q output low and the Q output high.