NB100LVEP221MNRG

2.5V/3.3V 2:1:20差分HSTL/ECL/PECL时钟驱动器

SMT扩展库SMT补贴嘉立创PCB免费打样

私有库下单最高享92折

- 描述

- NB100LVEP221 是一款低歪曲率 2:1:20 差分驱动器,适用于时钟分发,将两个时钟源接受到一个输入多路复用器中。两个时钟输入为差分 ECL/PECL;CLK1/CLK1bar 还可接收 HSTL 信号电平。LVPECL 输入信号可以为差分或单端(如果使用 VBB 输出)。LVEP221 专门保证输出对输出的低歪曲率。绝佳的设计、布局和处理技术将器件内部、器件到器件的歪曲率降到了最低。为了确保最严格的歪曲率,差分输出的两侧均同样端接到 50Ω,即使只使用一侧也是如此。如不使用某个输出对,可将两个输出保持开路(无端接),而不影响歪曲率。与大多数其他 ECL 器件一样,NB100LVEP221 可在 LVPECL 模式下由正向 VCC 电源供电。因此,在 +3.3 V 或 +2.5 V 系统中使用 LVEP221,可实现高性能的时钟分发。在 PECL 环境中,通常使用串行或戴维南线路终端,因为它们无需额外的电源。有关使用 PECL 端接的更多信息,设计人员应参考应用注释 AND8020/D。仅为此器件提供 VBB 引脚,即内部产生的供应电压。对于单端 LVPECL 输入的情况,将未使用的差分输入联接至 VBB,作为开关参考电压。VBB 还可将 AC 耦合输入重偏置。使用时,通过一个 0.01 uF 电容将 VBB 和 VCC 去耦合,并限制源或汲 0.5 mA 的电流。不使用时,VBB 应保持开路。单端 CLK 输入运行在 LVPECL 模式下仅限于 VCC >= 3.0 V,在 NECL 模式下仅限于 VEE <= -3.0 V。

- 品牌名称

- onsemi(安森美)

- 商品型号

- NB100LVEP221MNRG

- 商品编号

- C603344

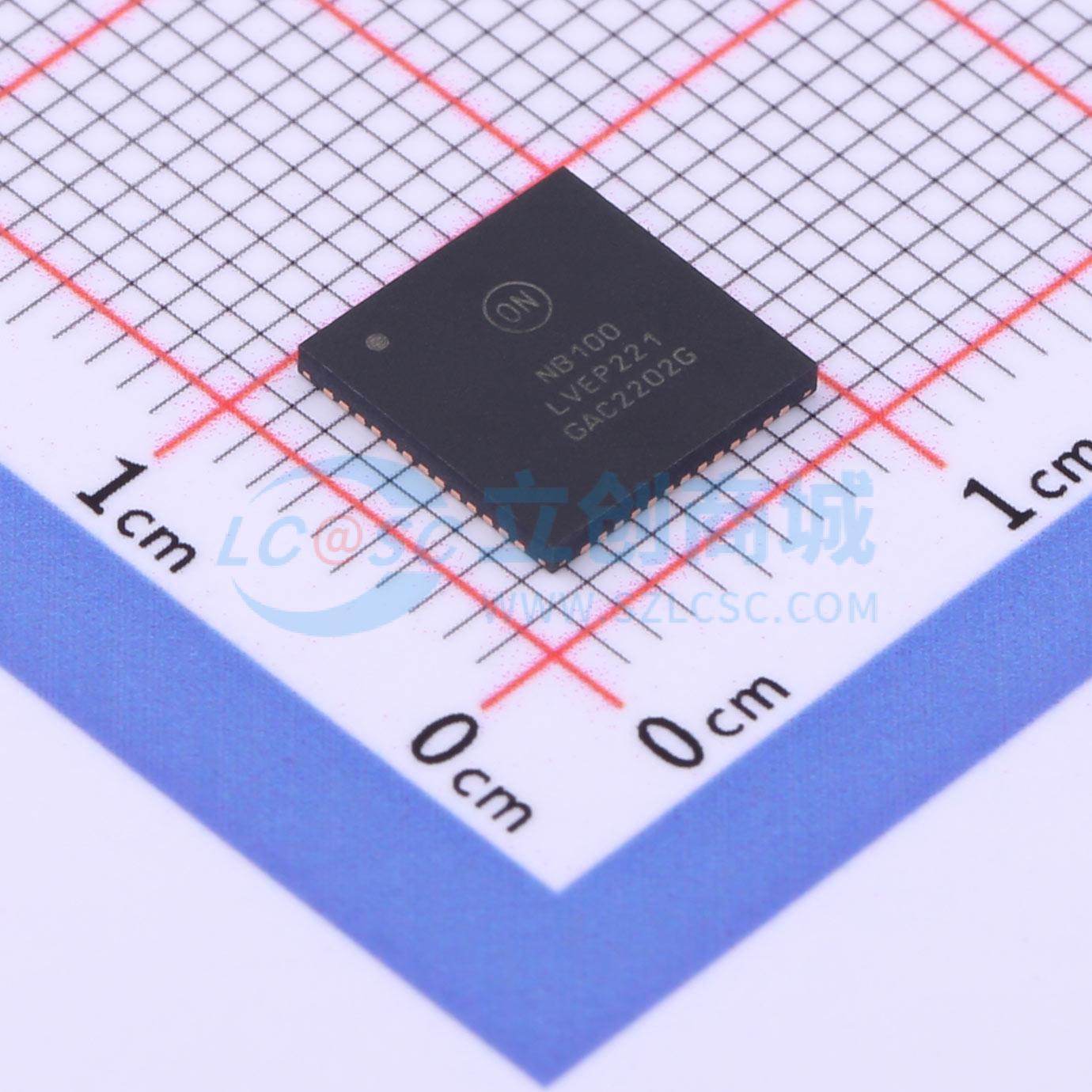

- 商品封装

- QFN-52(8x8)

- 包装方式

- 编带

- 商品毛重

- 0.45克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 时钟缓冲器/驱动器/分配器 | |

| 最大输出频率 | 1GHz | |

| 输入通道数 | 2 | |

| 输出通道数 | 20 |

| 属性 | 参数值 | |

|---|---|---|

| 工作电压 | 2.375V~3.8V | |

| 输出偏斜 | - | |

| 工作温度 | -40℃~+85℃ |

商品概述

NB100LVEP221是一款低偏斜2:1:20差分时钟驱动器,专为时钟分配设计,通过输入多路复用器接收两个时钟源。两个时钟输入为差分ECL/PECL;CLK1/CLK1也可接收HSTL信号电平。LVPECL输入信号可以是差分配置或单端配置(若使用VBB输出)。 LVEP221特别保证了低输出间偏斜。优化的设计、布局和工艺将器件内部及器件间的偏斜降至最低。 为确保最小偏斜,即使仅使用一个输出,差分输出的两端也应同样端接至50 Ω。若某一输出对未使用,两个输出可悬空(不端接),且不影响偏斜。 与大多数其他ECL器件一样,NB100LVEP221可在LVPECL模式下由正VCC电源供电。这使得LVEP221可用于+3.3 V或+2.5 V系统中的高性能时钟分配。在PECL环境中,通常使用串联或戴维南线路端接,因为它们无需额外电源。 VBB引脚是内部生成的电压源,仅为本器件提供。对于单端LVPECL输入情况,未使用的差分输入连接到VBB,作为开关参考电压。VBB也可为交流耦合输入重新偏置。使用时,通过0.01 μF电容对VBB和VCC去耦,并将源电流或灌电流限制在0.5 mA。不使用时,VBB应悬空。 在LVPECL模式下,单端CLK输入操作限于VCC ≥ 3.0 V;在NECL模式下,限于VEE ≤ -3.0 V。

商品特性

- 典型输出间偏斜:15 ps

- 典型器件间偏斜:40 ps

- 抖动:小于2 ps RMS

- 典型最大频率:>1.0 GHz

- 热增强型52引脚QFN封装

- VBB输出

- 典型传播延迟:540 ps

- LVPECL和HSTL模式工作范围:VCC = 2.375 V至3.8 V,VEE = 0 V

- NECL模式工作范围:VCC = 0 V,VEE = -2.375 V至-3.8 V

- 输入悬空或接VEE时,Q输出默认低电平

- 引脚与摩托罗拉MC100EP221兼容

- 这些器件无铅且符合RoHS标准