CA-IS3020WG

低功耗双向I²C隔离器

- 描述

- CA-IS302x 系列产品为完备的双向、双通道数字隔离器,提供 3.75kV_RMS(窄体封装)/5kV_RMS(宽体封装)/7.5kV_RMS(超宽体封装)电气隔离,以及高达 ±150kV/μs 的典型 CMTI。所有器件的输入采用施密特触发器,提高抗干扰能力。每个隔离通道的数字输入与输出通过二氧化硅 (SiO₂) 绝缘层隔离,提供较高的电磁干扰抑制和低 EMI 特性。高集成度设计仅需两个外部 VDDA、VDDB 旁路电容和上拉电阻,即可构成 I²C 隔离接口。这些双通道数字隔离器可支持 DC 至 2MHz 传输速率,CA-IS3020 提供两路双向、开漏输出隔离通道,用于支持多主机 I²C 等需要在同一总线双向传输数据或时钟的双向隔离应用;CA-IS3021 则提供一路单向和一路双向隔离通道,可支持单主机 I²C 隔离应用,单向通道用作时钟 (SCL) 隔离,双向通道用作数据 (SDA) 隔离。器件 A 侧 (V_DDA)、B 侧 (V_DDB) 单独供电,供电电压范围为 3.0V 至 5.5V。CA-IS302x 系列产品可工作在 -40°C 至 +125°C 温度范围,提供 8 引脚窄体 SOIC 封装、8 引脚/16 引脚宽体 SOIC 以及 8 引脚超宽体 SOIC 封装。由于较宽的工作温度范围和较高的隔离耐压,该系列器件适用于强干扰的工业环境。CA-IS302x 双通道数字隔离器提供完备的双向数字隔离方案,可承受高达 3.75kV_RMS(窄体封装)、5kV_RMS(宽体封装)以及 7.5kV_RMS(超宽体封装)的隔离电压,并具有 ±150kV/μs 典型 CMTI。这些双向数字隔离器不同于简单的两路单向隔离器并联方案,从根本上解决了低电平闭锁问题,且无需外部防死锁电路,有效节省尺寸和功耗。器件输入采用施密特触发器以提高抗干扰能力,数字通道的逻辑输入与输出之间采用电容隔离 (SiO₂)。该系列产品中,CA-IS3020 提供两路双向传输、开漏输出的数字隔离,以满足多主机 I²C 总线的数据、时钟隔离需求;CA-IS3021 包含 1 路单向传输通道和 1 路双向传输通道,分别用于单主机 I²C 总线中的时钟 (SCL) 和数据 (SDA) 线隔离。所有器件支持高达 2MHz 的数据速率,隔离器两侧的逻辑电平分别由电源电压 V_DDA、V_DDB 确定,供电范围为 3.0V 至 5.5V。CA-IS302x 采用电容隔离技术,与电感隔离相比,可提供更低功耗、更小的传输延时与信号抖动,具有更好的电磁辐射抑制,进而支持更高的信号传输速率。为了构建双向传输通道,CA-IS302x 在每个双向通道集成了两个单向通道,双向通道的输出采用漏极开路输出,以满足标准 I²C 接口的要求。其中,A 侧用于连接 I²C 节点的低电容负载,允许最大负载电容为 40pF;B 侧用于连接 I²C 总线节点的高电容负载,允许最大负载电容为 400pF。在双向传输隔离通道中,为了防止总线闭锁,A 侧输出采用一个特殊的缓冲器,将逻辑低电平输出电压调整在大约 700mV,而逻辑低电平输入的最高电压为 400mV。内部迟滞比较器通过检测 SDAA、SCLA 引脚的低电平电压,确定逻辑低电平是来自输入,还是隔离器的输出。通过比较器判断,可以避免将 A 侧输出的低电平错误地作为逻辑低电平输入而接受,并将其传送到 B 侧输出,由此规避了总线闭锁问题。隔离器 B 侧采用传统的缓冲器,不对逻辑低电平电压做任何调整。隔离器一侧的逻辑低电平输入将使另一侧对应引脚的电平拉低。I²C 总线通过 2 线接口实现不同 IC(系统控制器、远端传感器、激励器等电路)之间的数据通信,2 线接口包括一条数据线 (SDA) 和一条时钟线 (SCL),允许多个从机器件连接在同一总线,且不需要片选信号。由于总线上只有一条数据线,需要工作在半双工模式,即在任意时间段只能发送数据或只能接收数据,数据线需要支持双向传输。而对于多主机系统,则要求数据线和时钟线均支持双向传输。CA-IS302x 系列数字隔离器可提供两路双向传输通道(CA-IS3020)或一路用于数据的双向传输通道和一路用于时钟的单向传输通道(CA-IS3021),以满足 I²C 总线的隔离要求。I²C 总线工作在标准模式、快速模式或高速模式,最大速率分别对应于 100kbps、400kbps 和 1.7Mbps (C_bus = 400pF)。CA-IS302x 数字隔离器可支持最高 2MHz 的工作频率,满足绝大多数 I²C 应用的需求。CA-IS302x 隔离 IC 在两个不同的电源域提供完备的数字隔离,由于切断了接地环路,可以避免较高的共模干扰或故障电压损坏设备。这些器件不需要特殊的上电顺序,A、B 两侧信号的逻辑电平分别由 V_DDA 和 V_DDB 确定。SDAA、SCLA、SDAB、SCLB 引脚为开漏输出,需要通过外部上拉电阻连接至相应电源,以确保正确的逻辑高电平输出。B 侧输出可在 35mA 最大灌电流时确保正确的逻辑低电平;A 侧输出允许最大 3.5mA 的灌电流。由此,上拉电阻的最小值应确保 A 侧信号线输入电流 ≤3.5mA,B 侧信号线输入电流 ≤35mA。输入/输出线上拉电阻的最大值则取决于负载电阻和对上升时间的要求。为了减小电源纹波、降低干扰,电路设计中需要在 VDDA 引脚与 GNDA 之间,VDDB 引脚与 GNDB 之间分别安装一个至少 0.1μF 的低 ESR 电容。旁路电容应紧靠器件的电源引脚放置。除此之外,建议 PCB 使用尽可能短的输入、输出信号线,不要在信号线上使用过孔,以尽可能减小信号线上的寄生电感。隔离器下方不要布设任何地线或信号线,介于“A” 侧和“B” 侧之间的任何电气或金属连线都会降低隔离耐压。PCB 设计工程师应遵循这些基本要求,以获得最佳的数字隔离性能。

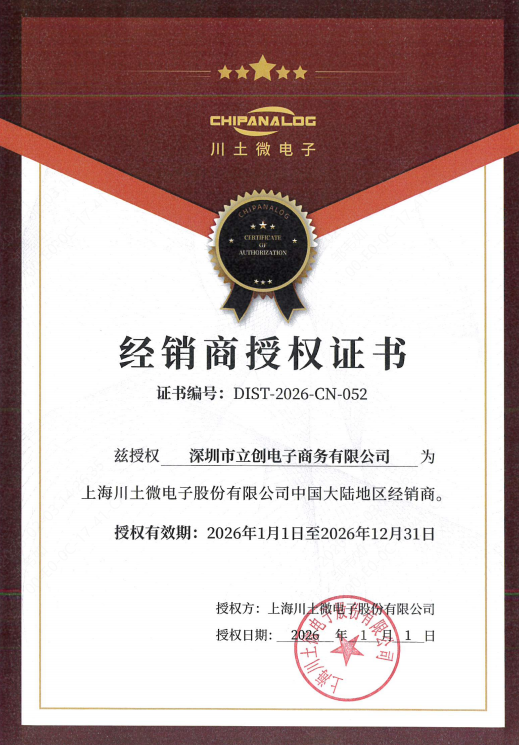

- 品牌名称

- Chipanalog(川土微)

- 商品型号

- CA-IS3020WG

- 商品编号

- C42370661

- 商品封装

- SOIC-8-WWB

- 包装方式

- 编带

- 商品毛重

- 0.501817克(g)

商品参数

参数完善中

商品概述

CA-IS302x 系列产品为完备的双向、双通道数字隔离器,提供 3.75kV_RMS(窄体封装)/5kV_RMS(宽体封装)/7.5kV_RMS(超宽体封装)电气隔离,以及高达 ±150kV/μs 的典型 CMTI。所有器件的输入采用施密特触发器,提高抗干扰能力。每个隔离通道的数字输入与输出通过二氧化硅 (SiO₂) 绝缘层隔离,提供较高的电磁干扰抑制和低 EMI 特性。高集成度设计仅需两个外部 VDDA、VDDB 旁路电容和上拉电阻,即可构成 I²C 隔离接口。 这些双通道数字隔离器可支持 DC 至 2MHz 传输速率,CA-IS3020 提供两路双向、开漏输出隔离通道,用于支持多主机 I²C 等需要在同一总线双向传输数据或时钟的双向隔离应用;CA-IS3021 则提供一路单向和一路双向隔离通道,可支持单主机 I²C 隔离应用,单向通道用作时钟 (SCL) 隔离,双向通道用作数据 (SDA) 隔离。器件 A 侧 (V_DDA)、B 侧 (V_DDB) 单独供电,供电电压范围为 3.0V 至 5.5V。 CA-IS302x 系列产品可工作在 -40°C 至 +125°C 温度范围,提供 8 引脚窄体 SOIC 封装、8 引脚/16 引脚宽体 SOIC 以及 8 引脚超宽体 SOIC 封装。由于较宽的工作温度范围和较高的隔离耐压,该系列器件适用于强干扰的工业环境。 CA-IS302x 双通道数字隔离器提供完备的双向数字隔离方案,可承受高达 3.75kV_RMS(窄体封装)、5kV_RMS(宽体封装)以及 7.5kV_RMS(超宽体封装)的隔离电压,并具有 ±150kV/μs 典型 CMTI。这些双向数字隔离器不同于简单的两路单向隔离器并联方案,从根本上解决了低电平闭锁问题,且无需外部防死锁电路,有效节省尺寸和功耗。器件输入采用施密特触发器以提高抗干扰能力,数字通道的逻辑输入与输出之间采用电容隔离 (SiO₂)。该系列产品中,CA-IS3020 提供两路双向传输、开漏输出的数字隔离,以满足多主机 I²C 总线的数据、时钟隔离需求;CA-IS3021 包含 1 路单向传输通道和 1 路双向传输通道,分别用于单主机 I²C 总线中的时钟 (SCL) 和数据 (SDA) 线隔离。所有器件支持高达 2MHz 的数据速率,隔离器两侧的逻辑电平分别由电源电压 V_DDA、V_DDB 确定,供电范围为 3.0V 至 5.5V。 CA-IS302x 采用电容隔离技术,与电感隔离相比,可提供更低功耗、更小的传输延时与信号抖动,具有更好的电磁辐射抑制,进而支持更高的信号传输速率。为了构建双向传输通道,CA-IS302x 在每个双向通道集成了两个单向通道,双向通道的输出采用漏极开路输出,以满足标准 I²C 接口的要求。其中,A 侧用于连接 I²C 节点的低电容负载,允许最大负载电容为 40pF;B 侧用于连接 I²C 总线节点的高电容负载,允许最大负载电容为 400pF。 在双向传输隔离通道中,为了防止总线闭锁,A 侧输出采用一个特殊的缓冲器,将逻辑低电平输出电压调整在大约 700mV,而逻辑低电平输入的最高电压为 400mV。内部迟滞比较器通过检测 SDAA、SCLA 引脚的低电平电压,确定逻辑低电平是来自输入,还是隔离器的输出。通过比较器判断,可以避免将 A 侧输出的低电平错误地作为逻辑低电平输入而接受,并将其传送到 B 侧输出,由此规避了总线闭锁问题。隔离器 B 侧采用传统的缓冲器,不对逻辑低电平电压做任何调整。隔离器一侧的逻辑低电平输入将使另一侧对应引脚的电平拉低。 I²C 总线通过 2 线接口实现不同 IC(系统控制器、远端传感器、激励器等电路)之间的数据通信,2 线接口包括一条数据线 (SDA) 和一条时钟线 (SCL),允许多个从机器件连接在同一总线,且不需要片选信号。由于总线上只有一条数据线,需要工作在半双工模式,即在任意时间段只能发送数据或只能接收数据,数据线需要支持双向传输。而对于多主机系统,则要求数据线和时钟线均支持双向传输。CA-IS302x 系列数字隔离器可提供两路双向传输通道(CA-IS3020)或一路用于数据的双向传输通道和一路用于时钟的单向传输通道(CA-IS3021),以满足 I²C 总线的隔离要求。I²C 总线工作在标准模式、快速模式或高速模式,最大速率分别对应于 100kbps、400kbps 和 1.7Mbps (C_bus = 400pF)。CA-IS302x 数字隔离器可支持最高 2MHz 的工作频率,满足绝大多数 I²C 应用的需求。 CA-IS302x 隔离 IC 在两个不同的电源域提供完备的数字隔离,由于切断了接地环路,可以避免较高的共模干扰或故障电压损坏设备。这些器件不需要特殊的上电顺序,A、B 两侧信号的逻辑电平分别由 V_DDA 和 V_DDB 确定。SDAA、SCLA、SDAB、SCLB 引脚为开漏输出,需要通过外部上拉电阻连接至相应电源,以确保正确的逻辑高电平输出。B 侧输出可在 35mA 最大灌电流时确保正确的逻辑低电平;A 侧输出允许最大 3.5mA 的灌电流。由此,上拉电阻的最小值应确保 A 侧信号线输入电流 ≤3.5mA,B 侧信号线输入电流 ≤35mA。输入/输出线上拉电阻的最大值则取决于负载电阻和对上升时间的要求。 为了减小电源纹波、降低干扰,电路设计中需要在 VDDA 引脚与 GNDA 之间,VDDB 引脚与 GNDB 之间分别安装一个至少 0.1μF 的低 ESR 电容。旁路电容应紧靠器件的电源引脚放置。除此之外,建议 PCB 使用尽可能短的输入、输出信号线,不要在信号线上使用过孔,以尽可能减小信号线上的寄生电感。隔离器下方不要布设任何地线或信号线,介于“A” 侧和“B” 侧之间的任何电气或金属连线都会降低隔离耐压。PCB 设计工程师应遵循这些基本要求,以获得最佳的数字隔离性能。

商品特性

- 支持 DC 至 2MHz 双向数据传输可靠的数字信号电气隔离

- 较长的工作寿命:>40 年

- 提供 3.75kV_RMS(窄体 SOIC)、5kV_RMS(宽体 SOIC)以及 7.5kV_RMS(超宽体 SOIC)电气隔离

- ±150kV/μs 典型 CMTI

- 施密特触发输入提高抗干扰能力

- 较高的电磁抑制,可承受最高 ±12.8kV 浪涌

- ±8kV ESD 保护(人体模式)

- 开漏输出:A 侧可支持最高 3.5mA 灌电流,B 侧可支持最高 35mA 灌电流

- 较宽的工作温度范围:-40°C to 125°C

- 提供多种 RoHS 兼容封装:窄体 SOIC8 (S) 封装、宽体 SOIC8 - WB (G) 封装、宽体 SOIC16 - WB (W) 封装、超宽体 SOIC8 - WWB (WG) 封装

- 安全认证:根据 DIN EN IEC60747 - 17(VDE 0884 - 17):2021 - 10 的 VDE 认证,根据 UL 1577 的 UL 认证,根据 GB4943.1 - 2022 的 CQC 认证

应用领域

- I²C, SMBus, PMBus 接口

- 电机控制系统

- 医疗设备

- 电池管理系统

- 仪器仪表