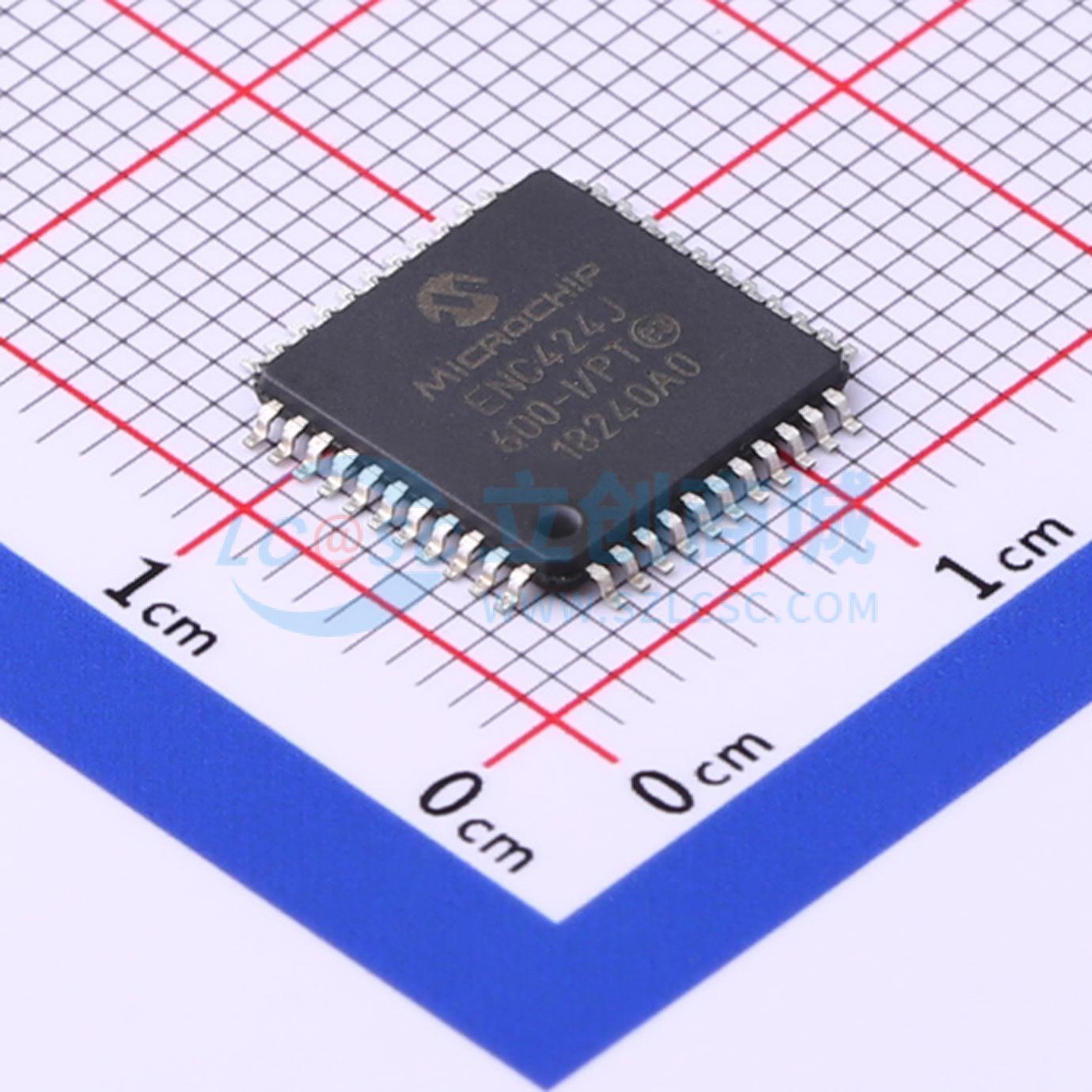

ENC424J600-I/PT

独立式10/100以太网控制器,支持SPI或并行接口

SMT扩展库PCB免费打样

私有库下单最高享92折

- 描述

- 独立的10/100以太网控制器,带有SPI或并行接口。符合IEEE 802.3标准的快速以太网控制器,集成MAC和10/100Base-T PHY,具备硬件安全加速引擎,拥有24KB的发送/接收数据包缓冲区SRAM,支持一个10/100Base-T端口,具备自动极性检测和校正功能,支持自动协商、暂停控制帧(包括自动发送和接收流量控制),支持半双工和全双工操作,可对冲突进行可编程自动重传,可编程填充和CRC生成,可编程自动拒绝错误和短数据包,具有工厂预编程的唯一MAC地址。

- 品牌名称

- MICROCHIP(美国微芯)

- 商品型号

- ENC424J600-I/PT

- 商品编号

- C13947

- 商品封装

- TQFP-44(10x10)

- 包装方式

- 托盘

- 商品毛重

- 1.499克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 以太网控制器 | |

| 通道数 | 1 | |

| MAC接口 | 并行;SPI | |

| 工作电压 | 3V~3.6V | |

| 集成PHY | 是 |

| 属性 | 参数值 | |

|---|---|---|

| 工作温度 | -40℃~+85℃ | |

| 通信接口 | SPI;并口 | |

| 存储空间 | 24KB | |

| 以太网速率标准 | 10BASE-T;100BASE-TX | |

| 数据速率 | 10Mbit/s;100Mbit/s |

商品特性

- 符合IEEE 802.3标准的快速以太网控制器

- 集成MAC和10/100Base-T PHY

- 硬件安全加速引擎

- 24KB的发送/接收数据包缓冲SRAM

- 支持一个10/100Base-T端口,具备自动极性检测与校正功能

- 支持自动协商

- 支持暂停控制帧,包括自动发送和接收流量控制

- 支持半双工和全双工操作

- 可编程的冲突自动重传功能

- 可编程的填充和CRC生成

- 可编程的错误和短数据包自动拒绝功能

- 工厂预编程的唯一MAC地址

- MAC:支持单播、多播和广播数据包;支持混杂模式接收;可编程模式匹配;支持对多种数据包格式进行可编程过滤,包括魔术包、单播、多播、广播、特定数据包匹配、目的地址哈希匹配或任意数据包

- PHY:波形整形输出滤波器;内部环回模式;能量检测掉电模式

- 可用的MCU接口:具有增强操作码集的14Mbit/s SPI接口(44引脚和64引脚封装);8位复用并行接口(44引脚和64引脚封装);8位或16位复用或解复用并行接口(仅64引脚封装)

- 安全引擎:高性能、支持最大1024位操作数的模幂运算引擎;支持RSA和Diffie-Hellman密钥交换算法;高性能AES加密/解密引擎,支持128位、192位或256位密钥;具备硬件AES ECB、CBC、CFB和OFB模式能力;软件AES CTR模式