HMC7044LP10BE

带 JESD204B 接口的高性能 3.2 GHz 14 路输出抖动衰减器

SMT扩展库SMT补贴嘉立创PCB免费打样

私有库下单最高享92折

- 描述

- 带JESD204B接口的高性能、3.2GHz、14路输出抖动衰减器

- 品牌名称

- ADI(亚德诺)

- 商品型号

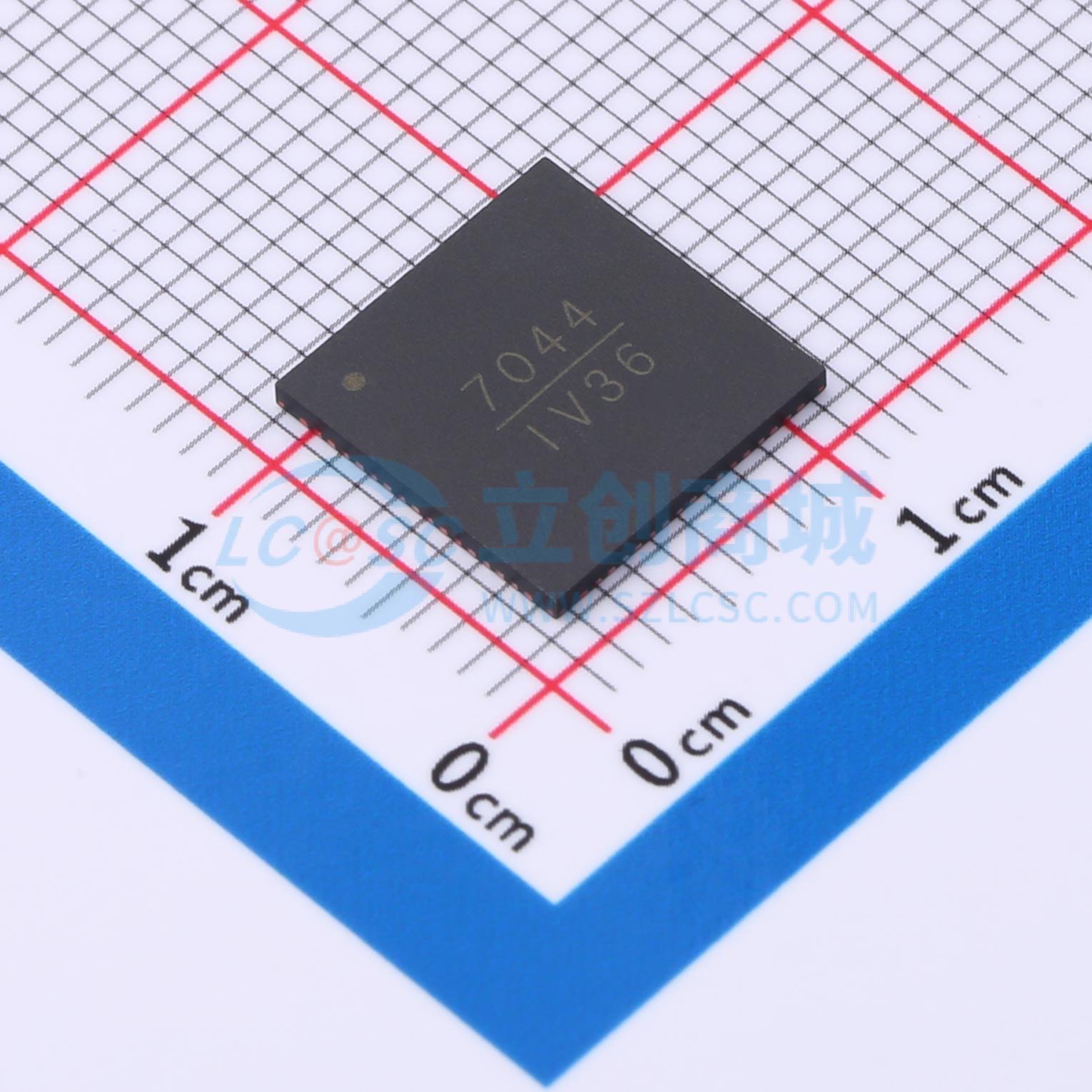

- HMC7044LP10BE

- 商品编号

- C579571

- 商品封装

- LFCSP-68(10x10)

- 包装方式

- 编带

- 商品毛重

- 0.668克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 时钟发生器/频率合成器/PLL | |

| 接口类型 | SPI | |

| 最大输出频率 | 3.2GHz | |

| 工作电压 | 3.135V~3.465V | |

| 输出通道数 | 14 | |

| 工作温度 | -40℃~+85℃ | |

| 周期抖动 | - |

| 属性 | 参数值 | |

|---|---|---|

| 相邻周期抖动 | - | |

| 相位抖动 | 108fs | |

| 相位偏移 | 支持 | |

| 时钟/振荡器 | 外置 | |

| 输入电平 | - | |

| 输出电平 | CMOS;LVDS;LVPECL;CML | |

| 功能特性 | - |

商品概述

HMC7044是一款高性能双环路整数N分频抖动衰减器,能够选择参考并生成超低相位噪声的频率,支持配有并行或串行(JESD204B型)接口的高速数据转换器。具有两个可通过SPI选择的整数模式PLL和交叠的片内VCO,调谐范围分别达2.5 GHz和3 GHz。该器件旨在满足GSM和LTE基站设计的要求,并通过多种时钟管理和分配特性来简化基带和无线电卡时钟树的设计。提供14路低噪声且可配置的输出,可以灵活地与许多不同器件接口,包括数据转换器、现场可编程门阵列(FPGA)和混频器本振(LO)。 HMC7044的DCLK和SYSREF时钟输出可配置来支持CML、LVDS、LVPECL和LVCMOS等信号标准,不同的偏置设置则可抵消变化的板插入损耗。

商品特性

- 超低rms抖动:典型值:44 fs(12 kHz至20 MHz,2457.6 MHz)噪底:−156 dBc/Hz (2457.6 MHz)

- 低相位噪声:−141.7 dBc/Hz(800 kHz时,983.04 MHz输出)

- PLL2最多提供14路LVDS、LVPECL或CML型器件时钟(DCLK)

- CLKOUTx/CLKOUTx和SCLKOUTx/SCLKOUTx频率最大值

- 各自都能对延迟进行编程

- 相位噪声与功耗的关系可通过SPI编程

- SYSREF有效中断可简化JESD204B同步

- 窄带、双核VCO

- 最多2个缓冲压控振荡器(VCXO)输出

- LVDS、LVPECL、CMOS和CML模式下最多4个输入时钟

- 频率保持模式可保持输出频率

- 信号丢失(LOS)检测和无中断参考切换

- 4个GPIO报警/状态指示器,可确定系统健康程度

- 支持最高6000 MHz的外部VCO输入

- 片内稳压器提供出色的PSRR

- 68引脚、10 mm × 10 mm LFCSP封装

应用领域

- JESD204B时钟产生

- 蜂窝基础设施(多载波GSM、LTE、W-CDMA)

- 数据转换器时钟

- 微波基带卡

- 相控阵参考分配