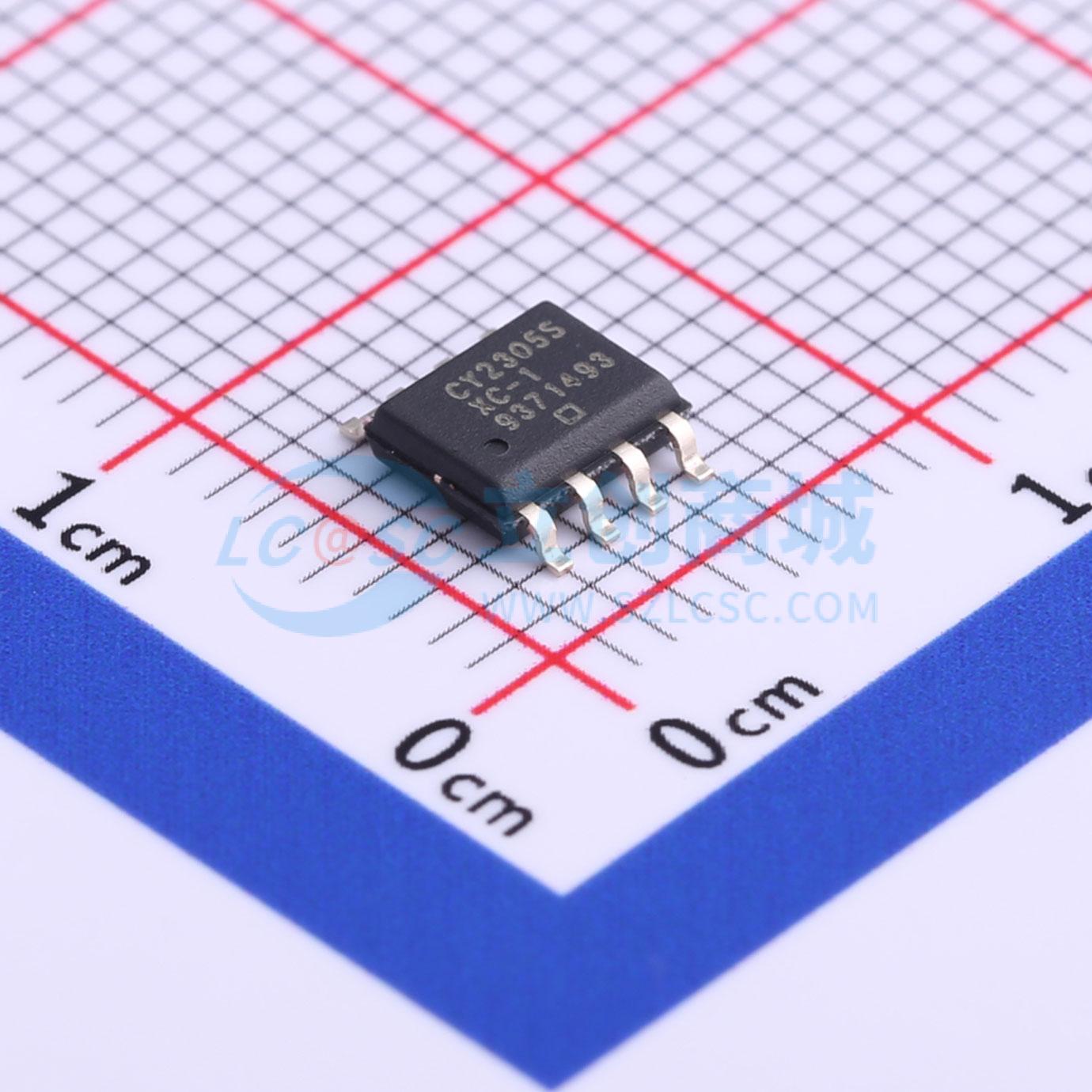

CY2305SXC-1T

Low Cost 3.3 V Zero Delay Buffer

SMT扩展库PCB免费打样

私有库下单最高享92折

- 描述

- 是一款低成本3.3V零延迟缓冲器,用于分配高速时钟,有8引脚和16引脚封装。它接受一个参考输入,并驱动五个低偏斜时钟。1H版本的每个设备工作频率高达100/133 MHz,并且比-1设备具有更高的驱动能力。所有部件都有片上锁相环 (PLL),可锁定REF引脚上的输入时钟。PLL反馈在片上,并从CLKOUT焊盘获得。

- 商品型号

- CY2305SXC-1T

- 商品编号

- C511128

- 商品封装

- SOIC-8

- 包装方式

- 编带

- 商品毛重

- 0.106克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 时钟缓冲器/驱动器/分配器 | |

| 最大输出频率 | 133.33MHz | |

| 工作电压 | 3V~3.6V |

| 属性 | 参数值 | |

|---|---|---|

| 工作温度 | 0℃~+70℃ | |

| 功能特性 | 内置锁相环 |

商品概述

CY2309是一款低成本的3.3 V零延迟缓冲器,旨在分配高速时钟,提供16引脚SOIC或TSSOP封装。CY2305是CY2309的8引脚版本,它接受一个参考输入,并驱动五个低偏斜时钟输出。每个器件的-1H版本可在高达100/133 MHz的频率下工作,且驱动能力比-1版本更强。所有器件都带有片上锁相环(PLL),可锁定REF引脚上的输入时钟。PLL反馈在片内完成,取自CLKOUT焊盘。 CY2309有两组输出,每组四个,可通过选择输入进行控制。若无需所有输出时钟,BankB可设置为三态。选择输入还允许将输入时钟直接应用于输出,用于芯片和系统测试。 当REF输入没有上升沿时,CY2305和CY2309的PLL进入掉电模式。在此状态下,输出为三态,PLL关闭,这些器件的电流消耗小于25.0 μA。CY2309的PLL在另一种情况下也会关闭。 多个CY2305和CY2309器件可接受相同的输入时钟并进行分配。在这种情况下,两个器件输出之间的偏斜保证小于700 ps。 CY2305/CY2309有两种或三种不同的配置。CY2305-1/CY2309-1是基础型号。CY2305-1H/CY2309-1H是-1型号的高驱动版本,其上升和下降时间比-1型号快得多。

商品特性

- 工作范围为10 MHz至100/133 MHz,与CPU和PCI总线频率兼容

- 输入输出零传播延迟

- 典型周期抖动为60 ps(高驱动)

- 多个低偏斜输出,典型输出间偏斜为85 ps

- 一个输入驱动五个输出(CY2305)

- 一个输入驱动九个输出,分组为4 + 4 + 1(CY2309)

- 与基于奔腾的系统兼容

- 测试模式可绕过锁相环(PLL)(CY2309)

- 封装:8引脚、150密耳SOIC封装(CY2305);16引脚、150密耳SOIC或4.4 mm TSSOP封装(CY2309)

- 3.3 V工作电压

- 商业和工业温度范围

其他推荐

- S29AL008J70BFI020

- CY8C21434-24LTXIT

- CY62148EV30LL-45ZSXIT

- S29GL512T10FHI010

- CY7C1041GN30-10ZSXI

- CY62148ELL-55SXIT

- CY8C27443-24SXI

- CY7C65632-48AXC

- CY8CMBR3108-LQXI

- CY62157EV30LL-45ZSXIT

- S29JL032J70TFI320

- S29GL128P10FFI010

- S25FL127SABMFI103

- CY62157EV30LL-45ZSXI

- CY8C27243-24PVXIT

- S29GL01GT10TFI020

- CY7C1021D-10ZSXIT

- CY62167EV30LL-45ZXIT

- FDMQ8203

- AMC1311BDWV

- ATmega32M1-AUR