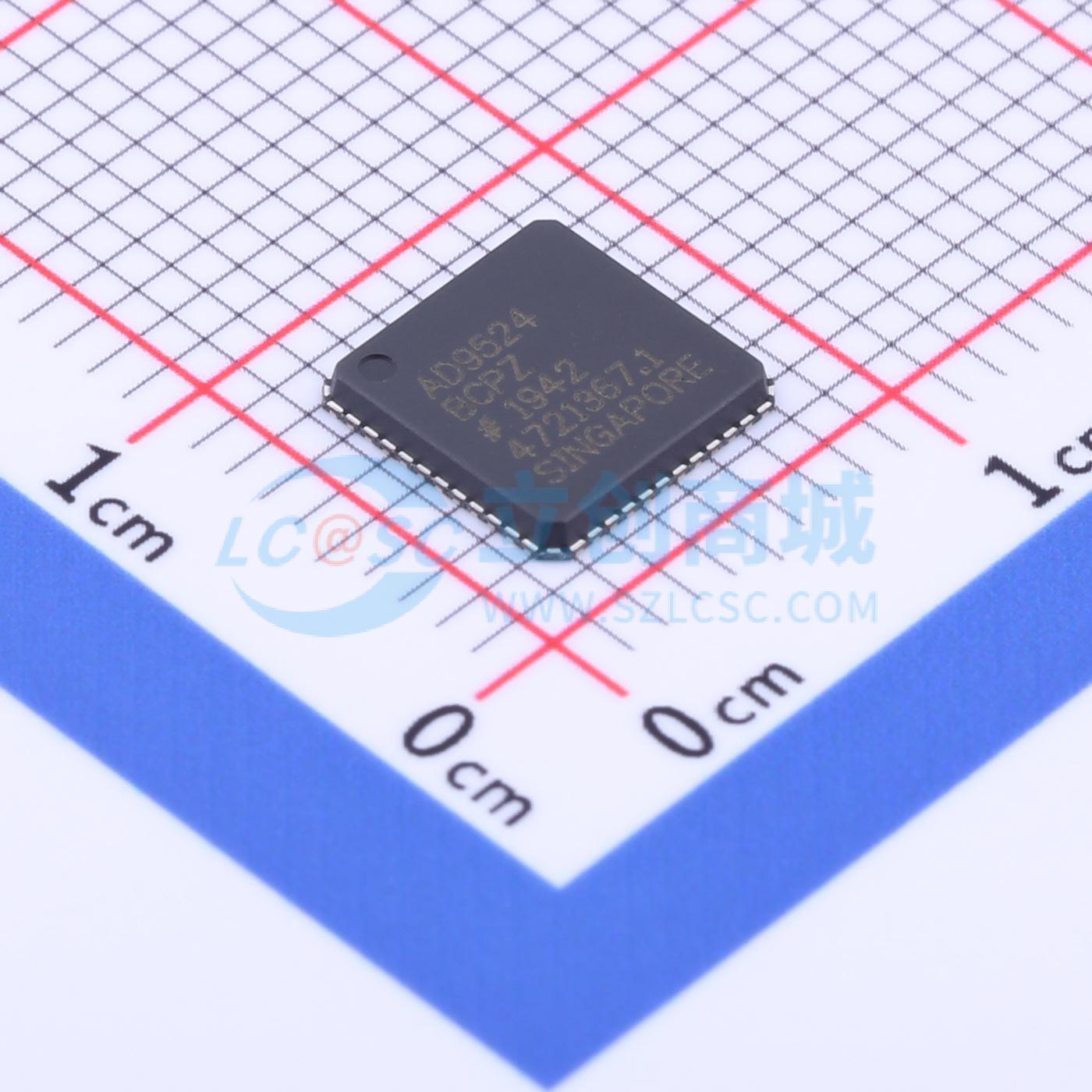

AD9524BCPZ

6路输出、双环路时钟发生器

SMT扩展库PCB免费打样

私有库下单最高享92折

- 描述

- AD9524 提供了一种低功耗、多输出的时钟分配功能,具有低抖动性能,并集成了片上PLL和VCO。片上VCO的调谐范围为3.6 GHz至4.0 GHz。AD9524 旨在支持长期演进(LTE)和多载波GSM基站设计的时钟需求。它依赖外部VCXO提供参考抖动清理,以达到满足数据转换器SNR性能所需的严格低相位噪声要求。输入接收器、振荡器和零延迟接收器既支持单端操作也支持差分操作。当连接到恢复的系统参考时钟和VCXO时,该器件生成六个低噪声输出,范围从1 MHz到1 GHz,以及一个来自输入PLL(PLL1)的专用缓冲输出。通过使用分频器相位选择功能,可以改变一个时钟输出相对于另一个时钟输出的频率和相位,该功能作为无抖动的粗略时序调整,增量等于VCO输出信号周期的一半。封装内的EEPROM可以通过串行接口编程,以存储用户定义的寄存器设置,用于上电和芯片复位。

- 品牌名称

- ADI(亚德诺)

- 商品型号

- AD9524BCPZ

- 商品编号

- C1520349

- 商品封装

- LFCSP-48-VQ(7x7)

- 包装方式

- 编带

- 商品毛重

- 2.9克(g)

商品参数

参数完善中

商品概述

AD9524 提供了一种低功耗、多输出的时钟分配功能,具有低抖动性能,并集成了片上PLL和VCO。片上VCO的调谐范围为3.6 GHz至4.0 GHz。

AD9524 旨在支持长期演进(LTE)和多载波GSM基站设计的时钟需求。它依赖外部VCXO提供参考抖动清理,以达到满足数据转换器SNR性能所需的严格低相位噪声要求。

输入接收器、振荡器和零延迟接收器既支持单端操作也支持差分操作。当连接到恢复的系统参考时钟和VCXO时,该器件生成六个低噪声输出,范围从1 MHz到1 GHz,以及一个来自输入PLL(PLL1)的专用缓冲输出。通过使用分频器相位选择功能,可以改变一个时钟输出相对于另一个时钟输出的频率和相位,该功能作为无抖动的粗略时序调整,增量等于VCO输出信号周期的一半。

封装内的EEPROM可以通过串行接口编程,以存储用户定义的寄存器设置,用于上电和芯片复位。

商品特性

- 输入到输出边缘定时: <±150 ps

- 6个输出: 可配置为LVPECL, LVDS, HSTL, 和 LVCMOS

- 6个专用输出分频器,具有无抖动的可调延迟

- 可调延迟: 63分辨率步长,占VCO周期的%周期

- 输出到输出偏斜: <±50 ps

- 奇数分频设置下的占空比校正

- 上电时所有输出自动同步

- 绝对输出抖动: <200 fs 在122.88 MHz

- 集成范围: 12 kHz 到 20 MHz

- 分布相位噪声底限: −160 dBc/Hz

- 数字锁定检测

- 非易失性EEPROM存储配置设置

- SPI和I2C兼容串行控制端口

- 双PLL架构

- PLL1

- 低带宽用于参考输入时钟清理,使用外部VCXO

- 相位检测速率高达130 MHz

- 冗余参考输入

- 自动和手动参考切换模式

- 恢复性和非恢复性切换

- 丢失参考检测并带有保持模式

- 用于RF/IF合成器的低噪声LVCMOS输出

- PLL2

- 相位检测速率高达259 MHz

- 集成低噪声VCO

应用领域

- LTE和多载波GSM基站

- 无线和宽带基础设施

- 医疗仪器

- 高速ADCs、DACs、DDSs、DDCs、DUCs、MxFEs的时钟

- 低抖动、低相位噪声时钟分配

- SONET、10Ge、10G FC及其他10 Gbps协议的时钟生成和转换

- 前向纠错(G.710)

- 高性能无线收发器

- ATE及高性能仪器