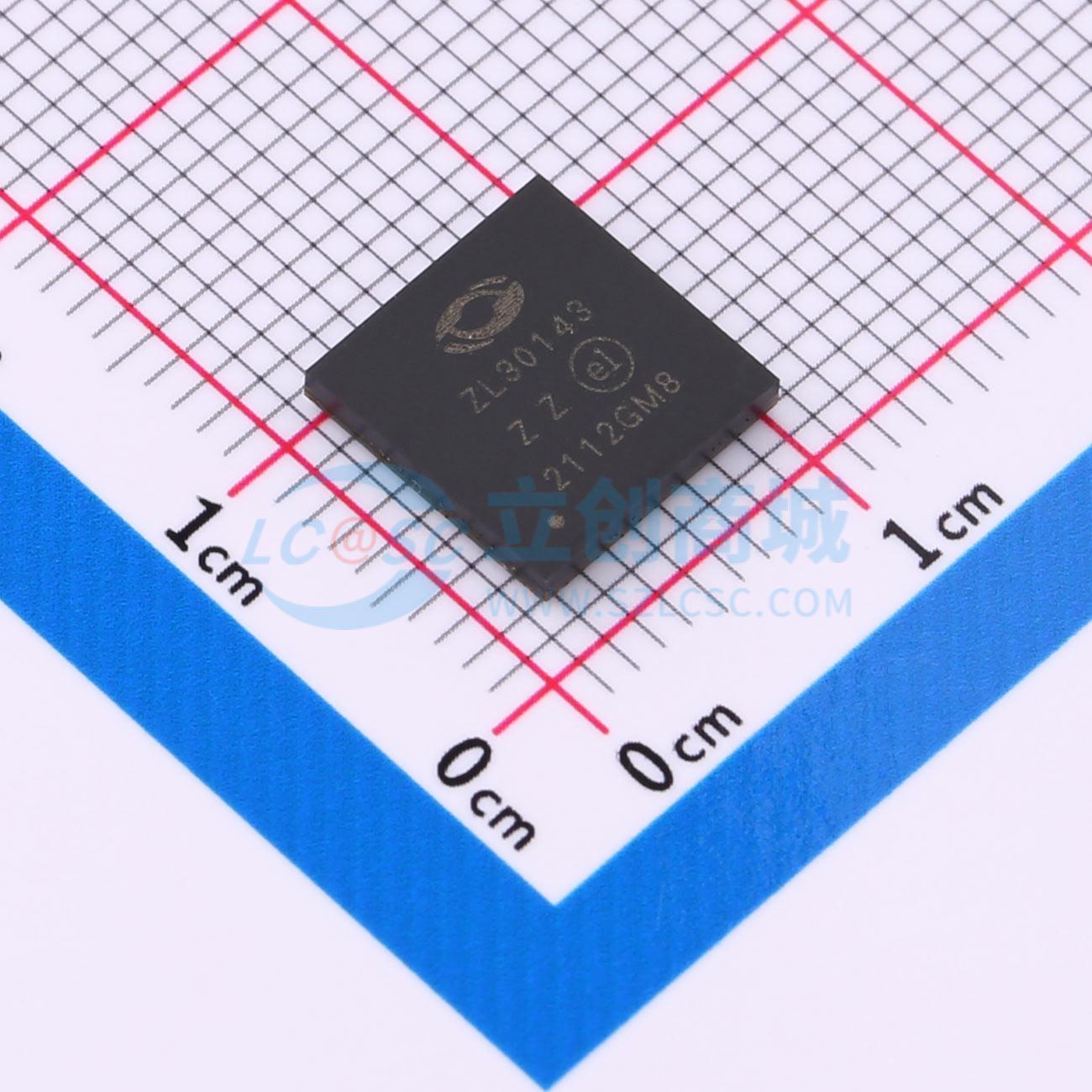

ZL30143GGG2

Sync E SONET/SDH G.8262/Stratum 3系统同步器/SETS

SMT扩展库PCB免费打样

私有库下单最高享92折

- 描述

- ZL30143系统同步器和SETS设备是一种高度集成的设备,为运营商级网络设备中的中央定时卡提供了所有必要的功能。中央定时卡的基本功能包括:- 对频率精度和相位不规则性的输入参考监控- 自动输入参考选择- 支持外部定时和线路定时模式- 无中断参考切换- 漫游和抖动过滤- 主/从交叉以最小化冗余定时卡之间的相位对齐- 独立的派生输出定时路径以支持SETS功能在典型应用中,主定时路径使用DPLL1与外部BITS源或恢复的线路定时源进行同步。DPLL1监控所有参考并根据可配置的优先级和回退属性自动选择最佳可用参考。DPLL1提供漫游过滤功能,P0合成器生成一个经过抖动过滤的时钟和帧脉冲,用于系统定时总线,该总线为所有线路卡提供一个共同的定时参考。APLL用于生成以太网PHY的参考时钟,可用于同步远程设备。还有一个使用DPLL2的派生输出定时路径来支持SETS功能。在这种情况下,DPLL2使用高于10 Hz的滤波器以防止其过滤漫游。

- 品牌名称

- MICROCHIP(美国微芯)

- 商品型号

- ZL30143GGG2

- 商品编号

- C1520353

- 商品封装

- CABGA-100(9x9)

- 包装方式

- 托盘

- 商品毛重

- 0.32克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 专用时钟/计时 |

| 属性 | 参数值 | |

|---|---|---|

| 功能特性 | 可编程时钟输出 |

商品概述

ZL30143系统同步器和SETS设备是一种高度集成的设备,为运营商级网络设备中的中央定时卡提供了所有必要的功能。中央定时卡的基本功能包括:

- 对频率精度和相位不规则性的输入参考监控

- 自动输入参考选择

- 支持外部定时和线路定时模式

- 无中断参考切换

- 漫游和抖动过滤

- 主/从交叉以最小化冗余定时卡之间的相位对齐

- 独立的派生输出定时路径以支持SETS功能

在典型应用中,主定时路径使用DPLL1与外部BITS源或恢复的线路定时源进行同步。DPLL1监控所有参考并根据可配置的优先级和回退属性自动选择最佳可用参考。DPLL1提供漫游过滤功能,P0合成器生成一个经过抖动过滤的时钟和帧脉冲,用于系统定时总线,该总线为所有线路卡提供一个共同的定时参考。APLL用于生成以太网PHY的参考时钟,可用于同步远程设备。还有一个使用DPLL2的派生输出定时路径来支持SETS功能。在这种情况下,DPLL2使用高于10 Hz的滤波器以防止其过滤漫游。

商品特性

- 支持 ITU-T G.8262 对同步以太网设备从时钟(EEC 选项 1 和 2)的要求

- 支持 Telcordia GR-1244 Stratum 3 和 GR-253、ITU-T G.813 和 G.781 SETS 的要求

- 支持 2048 kbit/s 和 1544 kbit/s 接口的 ITU-T G.823、G.824 和 G.8261

- 满足 SONET/SDH 抖动生成要求,最高可达 OC-48/STM-16

- 同步到电信参考时钟(2 KHz、N*8 kHz 最高 77.76 MHz、155.52 MHz)或以太网参考时钟(25 MHz、50 MHz、62.5 MHz、125 MHz)

- 支持复合时钟输入(64 kHz、64 kHz + 8 kHz、64kHz + 8 kHz + 400 Hz)

- 生成标准的 SONET/SDH 时钟速率(例如,19.44 MHz、38.88 MHz、77.76 MHz、155.52 MHz、622.08 MHz)或以太网时钟速率(例如,25 MHz、50 MHz、125 MHz、156.25 MHz、312.5 MHz),用于同步千兆以太网 PHY

- 可编程输出合成器(P0、P1)生成从任意 8 kHz 倍数到 100 MHz 的电信时钟频率

- 生成多种风格的电信帧脉冲,可选脉冲宽度、极性和频率

- 提供两个可通过串行接口独立配置的 DPLL

- 内部状态机自动控制工作模式(自由运行、锁定、保持)

- 灵活的输入参考监控根据频率和相位不规则性自动取消参考资格

- 在失去参考输入时提供自动参考切换和保持

- 支持主/从配置和动态输入到输出延迟补偿,适用于 AdvancedTCATM

- 可配置的输入到输出延迟和输出到输出相位对齐

应用领域

- 支持 1 GbE 和 10 GbE 接口的 ITU-T G.8262 系统时钟卡

- Telcordia GR-253 承载级 SONET/SDH Stratum 3 系统时钟卡

- 支持 ITU-T G.781 SETS (SDH 设备定时源) 的系统时钟卡

相似推荐

其他推荐