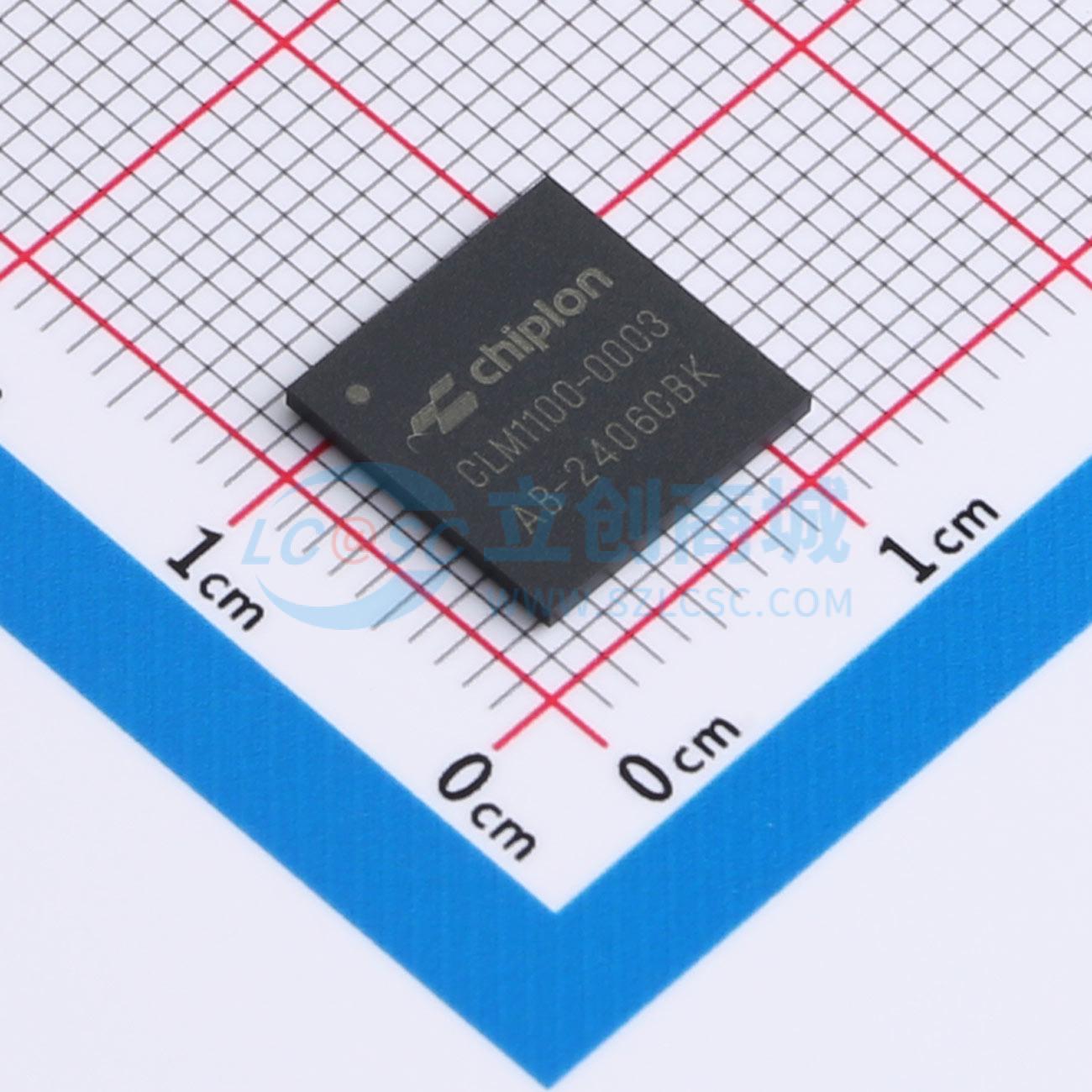

CLM1100-0003

ETHERCAT SLAVE CONTROLLER

- 描述

- 本芯片为工业以太网从站控制芯片,是实现工业以太网数据链路层协议的专用集成电路芯片。它处理工业以太网数据帧,并为从站控制装置提供数据接口。本芯片具有 4 个数据收发端口、8 个 FMMU 单元、8 个 SM 通道、4KB 控制寄存器、8KB 过程数据存储器、支持 64 位分布时钟功能。

- 品牌名称

- CHIPLON(启珑)

- 商品型号

- CLM1100-0003

- 商品编号

- C7433375

- 商品封装

- BGA-128(10x10)

- 包装方式

- 托盘

- 商品毛重

- 3.32233克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 以太网收发器 | |

| 类型 | - | |

| 端口数量 | 4 | |

| MAC接口 | MII | |

| 以太网速率标准 | - |

| 属性 | 参数值 | |

|---|---|---|

| 数据速率 | 100Mbit/s | |

| 工作电压 | 3.3V;5V | |

| 功耗 | - | |

| 工作温度 | - |

商品概述

本芯片为工业以太网从站控制芯片,是实现工业以太网数据链路层协议的专用集成电路芯片。它处理工业以太网数据帧,并为从站控制装置提供数据接口。 本芯片具有 4 个数据收发端口、8 个 FMMU 单元、8 个 SM 通道、4KB 控制寄存器、8KB 过程数据存储器、支持 64 位分布时钟功能。它可以直接作为 32 位数字量输入/输出站点,或由外部微处理器控制,组成复杂的从站设备。 本芯片有 4 个物理通信端口,分别命名为端口 0 到端口 3,每个端口都可以配置为 MII 接口或 LVDS 接口两种形式。 MII 接口:使用此接口时,需要外接以太网物理层 PHY 芯片。 LVDS 接口:使用低压差分信号,最远传输距离为 10 米。 支持直接 IO 信号接口、SPI 接口、并行/串行微处理器接口。 每个以太网从站控制器可以最多支持 4 个数据收发端口,每个端口都可以处在打开或闭合状态。如果端口打开,则可以向其他以太网从站控制器发送数据帧或从其他以太网从站控制器接收数据帧。一个闭合的端口不会与其他以太网从站控制器交换数据帧,它在内部将数据帧转发到下一个逻辑端口,直到数据帧到达一个打开的端口。 以太网从站控制器使用了存储同步管理通道 SM(SyncManager)来保证主站与本地应用数据交换的一致性和安全性,并在数据状态改变时产生中断来通知双方。 FMMU 将从站本地物理存储地址映射到网段内逻辑地址。实现从站在 4GB(232)地址空间的逻辑寻址,报文内的 32 位地址区作为整体的数据逻辑寻址的地址。 分布时钟(DC,Distributed Clock)可以使所有工业以太网设备使用相同的系统时间,从而控制设备任务的同步执行。从站设备可以根据同步的系统时间产生同步信号,用于中断控制或触发数据量输入输出。 CLM1100 支持不同的电源和 I/O 电平选择,它可以是 3.3V(也可选用 5V,但是实际应用中不建议选用),也支持选择单电源供电或者双电源供电。 VCC I/O 的电压值直接决定所有 I/O 信号的电平,它可以使用 3.3V 或 5V 供电。使用 3.3V 时,I/O 信号电平即为 3.3V,不允许使用 5V 输入。使用 5V 供电时,I/O 信号电平即为 5V。 CLM1100 逻辑内核要求 1.8V 供电。VCC Core/VCC PLL 可通过内部 LDO(Low Dropout Regulator,低压线性稳压器)产生,也可由外部提供。内部 LDO 使用 VCC I/O 作为电源。VCC Core 总等于 VCC PLL。内部 LDO 不能被关闭,但是如果外部供电电压高于内部 LDO 输出时,LDO 停止供电,因此 VCC Core/VCC PLL 使用外部供电时,供电电压至少要高于内部 LDO 电压输出 0.1V,以使内部 LDO 停止输出。 使用内部 LDO 会增加功耗,同时值得注意的是,I/O 信号选用 5V 供电时的功耗大于 I/O 信号选用 3.3V 供电时的功耗。所以建议选用 3.3V 的 I/O 信号电压和内部 LDO 为 VCC Core/VCC PLL 供电。 每个电源引脚都要连接稳压电容。 根据需要的接口电压,VCC I/O 电源管脚可以使用 3.3V 或者 5V 供电(不推荐使用 5V)。使用 3.3V 供电时,I/O 信号电平即为 3.3V,不允许使用 5V 输入。使用 5V 供电时,I/O 信号电平即为 5V。所有的电源引脚 VCC I/O/GNDI/O 之间必须并联稳压电容。 CLM1100 的逻辑内核要求 1.8V 供电,该供电电压既可以由内部 LDO 产生,也可以由外部提供。内部 LDO 使用 VCC I/O 作为电源供电。这两种情况下,电源引脚 VCC Core/GNDCore 之间必须并联稳压电容。 PLL(Phase Lock Loop,锁相回路)电源供电电压 1.8V,该供电电压既可以由内部 LDO 产生,也可以由外部提供。内部 LDO 使用 VCC I/O 作为电源供电。这两种情况下,电源引脚 VccPLL/GNDPLL 之间必须并联稳压电容。 引脚 OSC_IN 作为时钟源输入,外接 25MHz 的晶体或者振荡器。当 CLM1100 的时钟由振荡器提供时,以太网 PHY 芯片的时钟需由 CLM1100 输出时钟提供,具体使用方法参考引脚配置章节。25MHz 的时钟源要求精度为 25ppm 以上。 管脚 RESET 是集电极开路输入/输出信号(低电平有效),表示 CLM1100 的复位状态,以下三种情况可以引起 CLM1100 内部复位:

- 在上电之后进入复位状态;

- 供电电压过低;

- 由写复位寄存器 0x0040 触发一次复位。 RESET 信号可以用于复位其它外围芯片。