SY100EP195VTG

3.3V/5V 1.6 GHz 可编程延迟线

SMT扩展库PCB免费打样

私有库下单最高享92折

- 描述

- 是可编程延迟线,可改变逻辑信号从 IN 到 Q 的传输时间。该延迟范围约为 2.1 ns 至 10.8 ns。输入可以是 PECL、LVPECL、NECL 或 LVNECL。延迟根据提供给设备的控制字以离散步骤变化。这个锁存控制寄存器的 10 位宽度允许大约 10 ps 的延迟增量。第十一个控制位允许级联多个设备,以实现更宽的延迟范围。每个额外的设备有效地使可用延迟范围加倍。为了实现最大的灵活性,控制寄存器接口接受 CMOS 或 TTL 电平信号,以及 IN、/IN 引脚的输入电平。

- 品牌名称

- MICROCHIP(美国微芯)

- 商品型号

- SY100EP195VTG

- 商品编号

- C633767

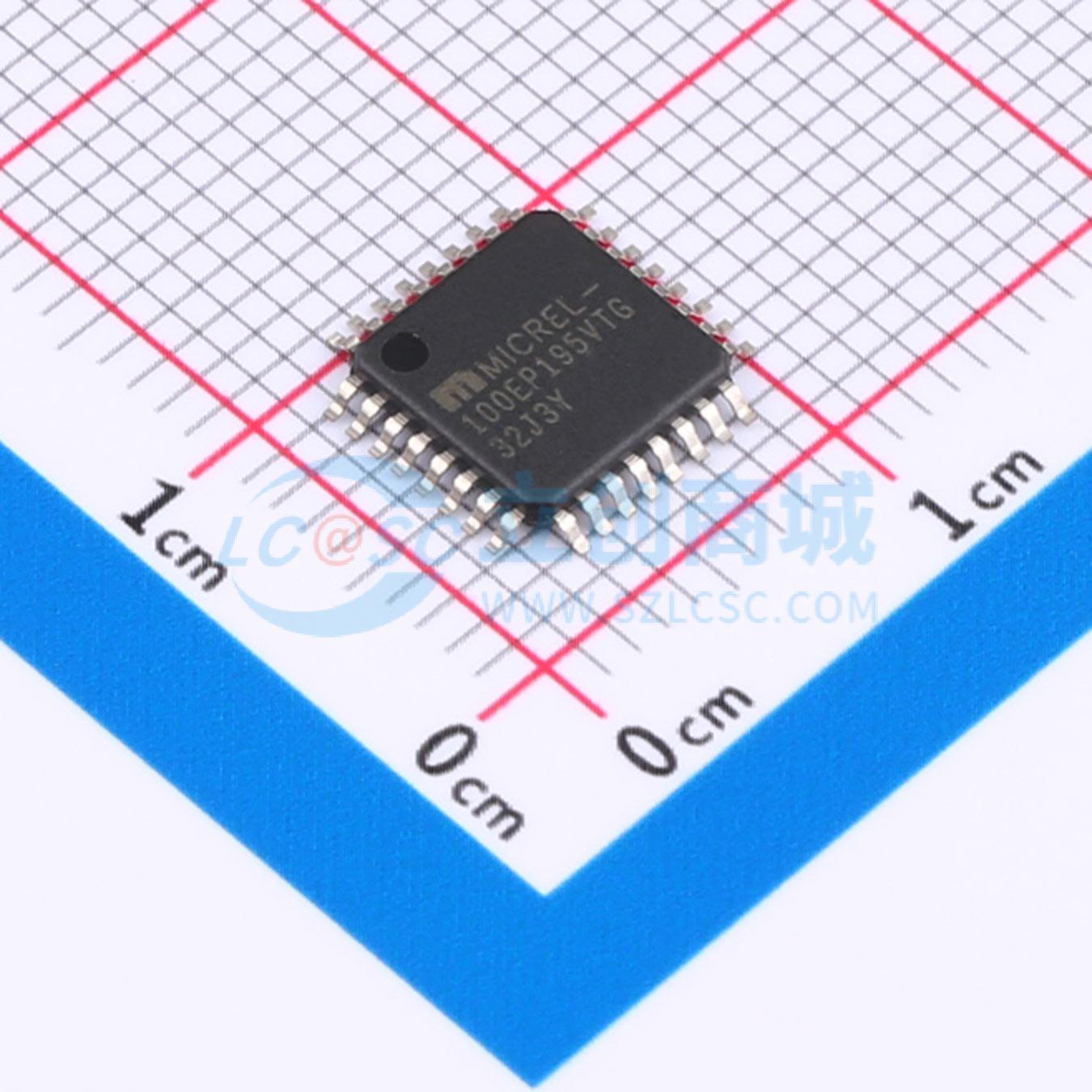

- 商品封装

- TQFP-32(7x7)

- 包装方式

- 托盘

- 商品毛重

- 0.12克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 时钟延迟 | |

| 可用总延迟范围 | 2.05ns~12.2ns | |

| 工作电压 | 3V~5.5V |

| 属性 | 参数值 | |

|---|---|---|

| 工作温度 | -40℃~+85℃ | |

| 功能特性 | 可编程时钟延迟;细粒度延迟步进 |

商品概述

SY100EP195V是一款可编程延迟线,可改变逻辑信号从IN端传输到Q端所需的时间。该延迟时间可在约2.1ns至约10.8ns之间变化。输入信号可以是PECL、LVPECL、NECL或LVNECL。 延迟时间根据提供给SY100EP195V的控制字以离散步长变化。这个锁存控制寄存器的10位宽度允许延迟增量约为10ps。 第11个控制位允许级联多个SY100EP195V器件,以实现更宽的延迟范围。每增加一个SY100EP195V,有效延迟范围将翻倍。 为实现最大灵活性,控制寄存器接口可接受CMOS或TTL电平信号,以及IN、/IN引脚的输入电平信号。

商品特性

- 与安森美半导体MC100EP195引脚兼容、可直接插拔替换

- 最高频率 >1.6 GHz

- 可编程范围:2.1 ns至10.8ns

- 10ps增量

- PECL模式工作范围:VCC = 3.0V至5.5V,VEE = 0V

- NECL模式工作范围:VCC = 0V,VEE = -3.0V至 -5.5V

- 输入开路默认状态

- 输入安全钳位

- /EN引脚为逻辑高电平时将强制Q端为逻辑低电平

- D[0:10]可接受ECL、CMOS或TTL输入

- VBB输出参考电压

- 采用32引脚TQFP封装

应用领域

- 时钟去偏斜

- 时序调整

- 孔径居中