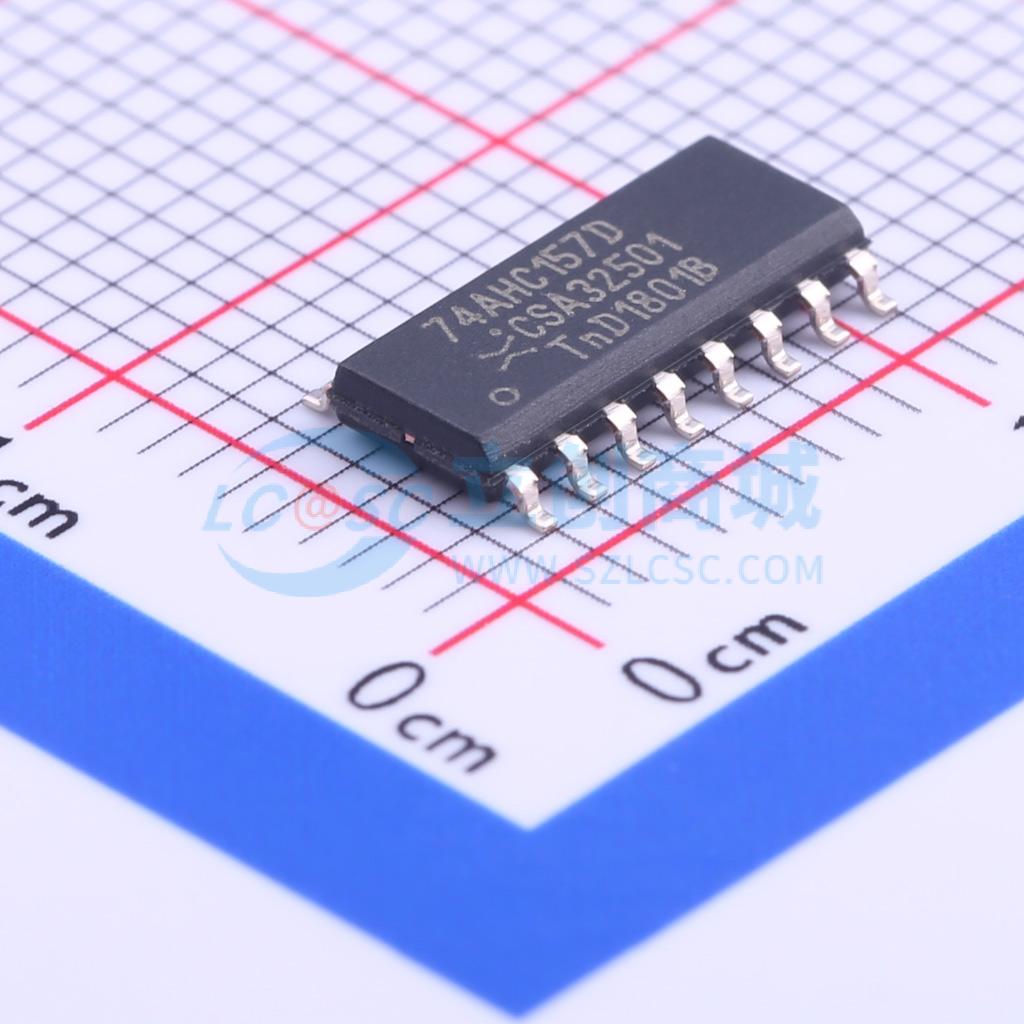

74AHC157D

74AHC157D

SMT扩展库PCB免费打样

私有库下单最高享92折

- 品牌名称

- Nexperia(安世)

- 商品型号

- 74AHC157D

- 商品编号

- C5511

- 商品封装

- SOIC-16

- 包装方式

- 袋装

- 商品毛重

- 0.276克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 信号开关/编解码器/多路复用器 | |

| 类型 | - | |

| 电源极性 | - | |

| 工作电压 | 2V~5.5V | |

| 输入数/输出数 | - | |

| 灌电流(IOL) | 8mA |

| 属性 | 参数值 | |

|---|---|---|

| 拉电流(IOH) | 8mA | |

| 工作温度 | -40℃~+85℃ | |

| 传播延迟(tpd) | 3.2ns@5V,15pF | |

| 静态电流(Iq) | 4uA | |

| 功能特性 | - |

商品概述

74AHC/AHCT157 是高速硅栅 CMOS 器件,与低功耗肖特基 TTL(LSTTL)引脚兼容。它们符合 JEDEC 标准 No. 7A。74AHC/AHCT157 是四路 2 输入多路复用器,在一个公共数据选择输入 (S) 的控制下从两个源中选择 4 位数据。使能输入 (E) 为低电平有效。当 E 为高电平时,所有输出 (1Y 至 4Y) 不论其他输入条件如何都强制为低电平。将两组寄存器的数据移动到四个公共输出总线是‘157’的一个常见用途。公共数据选择输入 (S) 的状态决定了数据来源的特定寄存器。它也可以作为函数发生器使用,通过生成具有一个共同变量的两个变量的 16 种不同函数中的任意四种来实现高度不规则的逻辑。

该器件可以实现一个 4 极、2 位置开关的逻辑功能,其中开关的位置由应用于 S 的逻辑电平决定。逻辑方程为:1Y = E x (1I1 x S + 1I0 x S̄);2Y = E x (2I1 x S + 2I0 x S̄);3Y = E x (3I1 x S + 3I0 x S̄);4Y = E x (4I1 x S + 4I0 x S̄)。‘157’与‘158’相同,但具有非反相(真)输出。

商品特性

- ESD 保护:HBM EIA/JESD22-A114-A 超过 2000 V,MM EIA/JESD22-A115-A 超过 200 V,CDM EIA/JESD22-C101 超过 1000 V

- 平衡的传播延迟

- 所有输入具有施密特触发动作

- 多个输入使能便于扩展

- 适用于存储器芯片选择解码

- 输入可接受高于 VCC 的电压

- 仅对于 AHC:与 CMOS 输入电平兼容

- 仅对于 AHCT:与 TTL 输入电平兼容

- 工作温度范围为 -40 至 +85 和 +125°C

应用领域

- 适用于内存芯片选择解码

- 将两组寄存器的数据移动到四个公共输出总线

- 可用于实现高度不规则的逻辑,通过生成两个变量(其中一个变量相同)的16种不同函数中的任意四种来实现

- 四极双位开关的逻辑实现