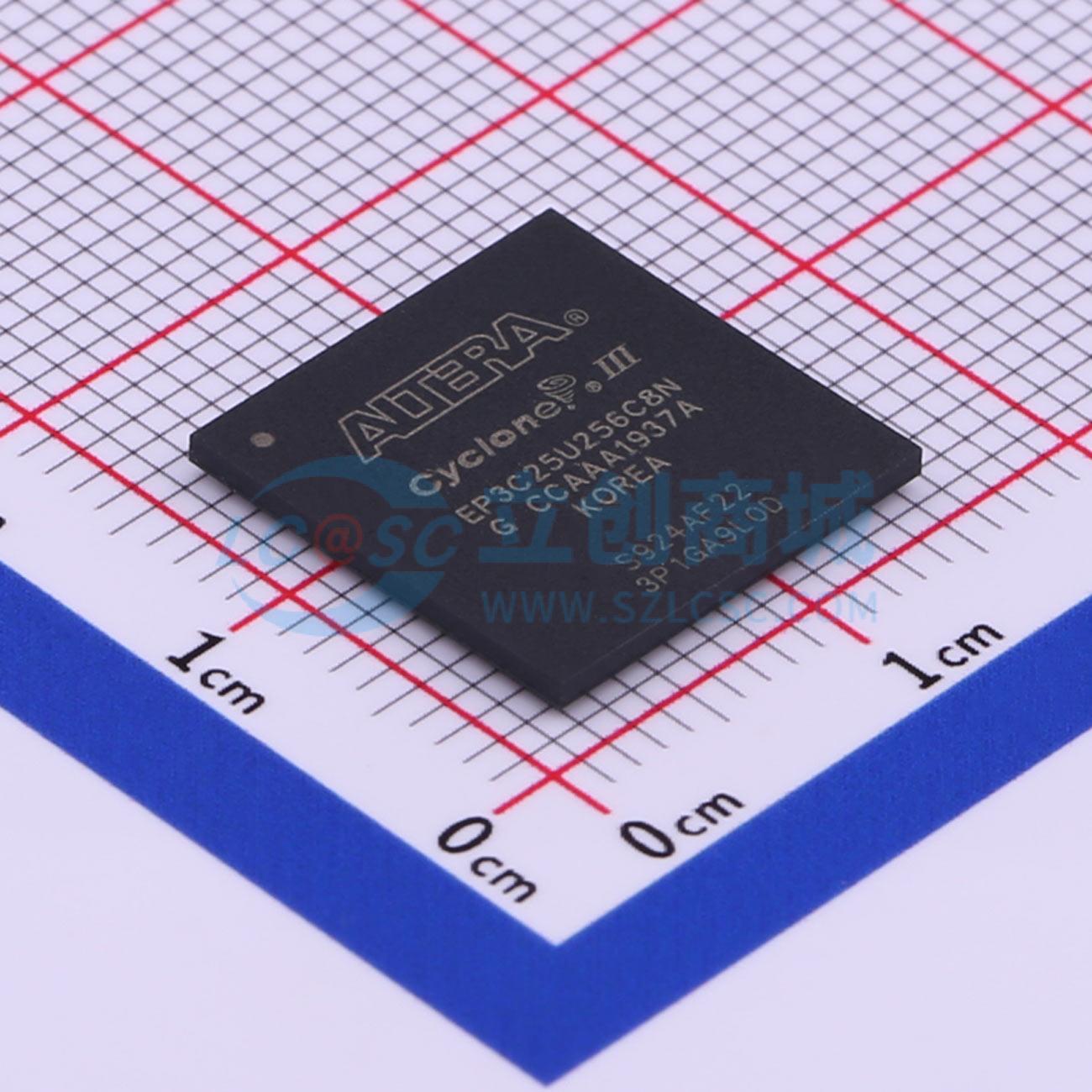

EP3C25U256C8N

EP3C25U256C8N

SMT扩展库PCB免费打样

私有库下单最高享92折

- 品牌名称

- Intel/Altera

- 商品型号

- EP3C25U256C8N

- 商品编号

- C568973

- 商品封装

- UBGA-256

- 包装方式

- 托盘

- 商品毛重

- 0.53克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 可编程逻辑器件(CPLD/FPGA) | |

| 类型 | - | |

| 工作电压(VCCIO) | - | |

| 逻辑单元数 | 24624 |

| 属性 | 参数值 | |

|---|---|---|

| 逻辑阵列块数量 | 1539 | |

| 内嵌式块RAM(eRAM) | 608256bit | |

| 工作温度 | 0℃~+85℃ | |

| 功能特性 | 支持SEU检错纠错;支持多版本位流回退功能;支持热插拔;支持AES加密 |

商品特性

- 功耗最低的FPGA

- 设计安全特性

- 增强的系统集成能力

- 逻辑单元和逻辑阵列块

- 存储块

- 嵌入式乘法器和数字信号处理支持

- 时钟网络和PLL

- I/O特性

- 高速差分接口

- 自动校准外部存储器接口

- 支持行业标准嵌入式处理器

- 热插拔和上电复位

- 单粒子翻转缓解

- JTAG边界扫描测试

- Quartus II软件支持

- 配置

- 远程系统升级

- 设计安全(仅适用于Cyclone III LS器件)

- 逻辑单元特性

- 逻辑单元工作模式:正常模式、算术模式

- 控制信号

- 奇偶校验位支持

- 字节使能支持

- 打包模式支持

- 地址时钟使能支持

- 混合宽度支持

- 异步清零

- 存储模式:单端口模式、简单双端口模式、真双端口模式、移位寄存器模式、ROM模式、FIFO缓冲模式

- 时钟模式:独立时钟模式、I/O时钟模式、读或写时钟模式、单时钟模式

- 设计注意事项:写操作期间读操作、同端口写操作期间读模式、混合端口写操作期间读模式、冲突解决、上电条件和存储器初始化、电源管理

- 嵌入式乘法器块概述

- 架构:输入寄存器、乘法器级、输出寄存器

- 操作模式:18位乘法器、9位乘法器

- 时钟网络:GCLK网络、时钟控制块、GCLK网络时钟源生成、GCLK网络掉电、clkena信号

- Cyclone III器件系列中的PLL:Cyclone III器件系列PLL硬件概述、外部时钟输出、时钟反馈模式:源同步模式、无补偿模式、正常模式、零延迟缓冲模式

- 硬件特性:时钟乘法和除法、后置分频计数器级联、可编程占空比

- PLL控制信号:pfdena、areset、locked

- 时钟切换:自动时钟切换、手动覆盖、手动时钟切换

- 指南

- 可编程带宽

- 相移实现

- PLL级联

- PLL重新配置

- PLL重新配置硬件实现

- 后置分频计数器(C0至C4)

- 扫描链描述

- 电荷泵和环路滤波器

- 旁路PLL计数器

- 动态相移

- 扩频时钟

- Cyclone III器件系列I/O单元

- I/O单元特性:可编程电流强度、压摆率控制、开漏输出、总线保持、可编程上拉电阻、可编程延迟、PCI钳位二极管、LVDS发射器可编程预加重、OCT支持、带校准的片上串联端接、不带校准的片上串联端接

- I/O标准

- I/O标准的端接方案:电压参考I/O标准端接、差分I/O标准端接

- I/O组

- 高速差分接口

- 外部存储器接口

- 焊盘布局和直流指南:焊盘布局、直流指南

- 高速I/O接口

- 高速I/O标准支持:LVDS I/O标准支持、BLVDS I/O标准支持、RSDS、Mini-LVDS和PPDS I/O标准支持、LVPECL I/O支持、差分SSTL I/O标准支持、差分HSTL I/O标准支持

- 真输出缓冲特性

- 可编程预加重

- 高速I/O时序

- 设计指南:差分焊盘布局指南、电路板设计注意事项

- 软件概述

- Cyclone III器件系列存储器接口引脚支持:数据和数据时钟/选通引脚、可选奇偶校验、DM和纠错编码引脚、地址和控制/命令引脚、存储器时钟引脚

- Cyclone III器件系列存储器接口特性:DDR输入寄存器、DDR输出寄存器、OCT、PLL