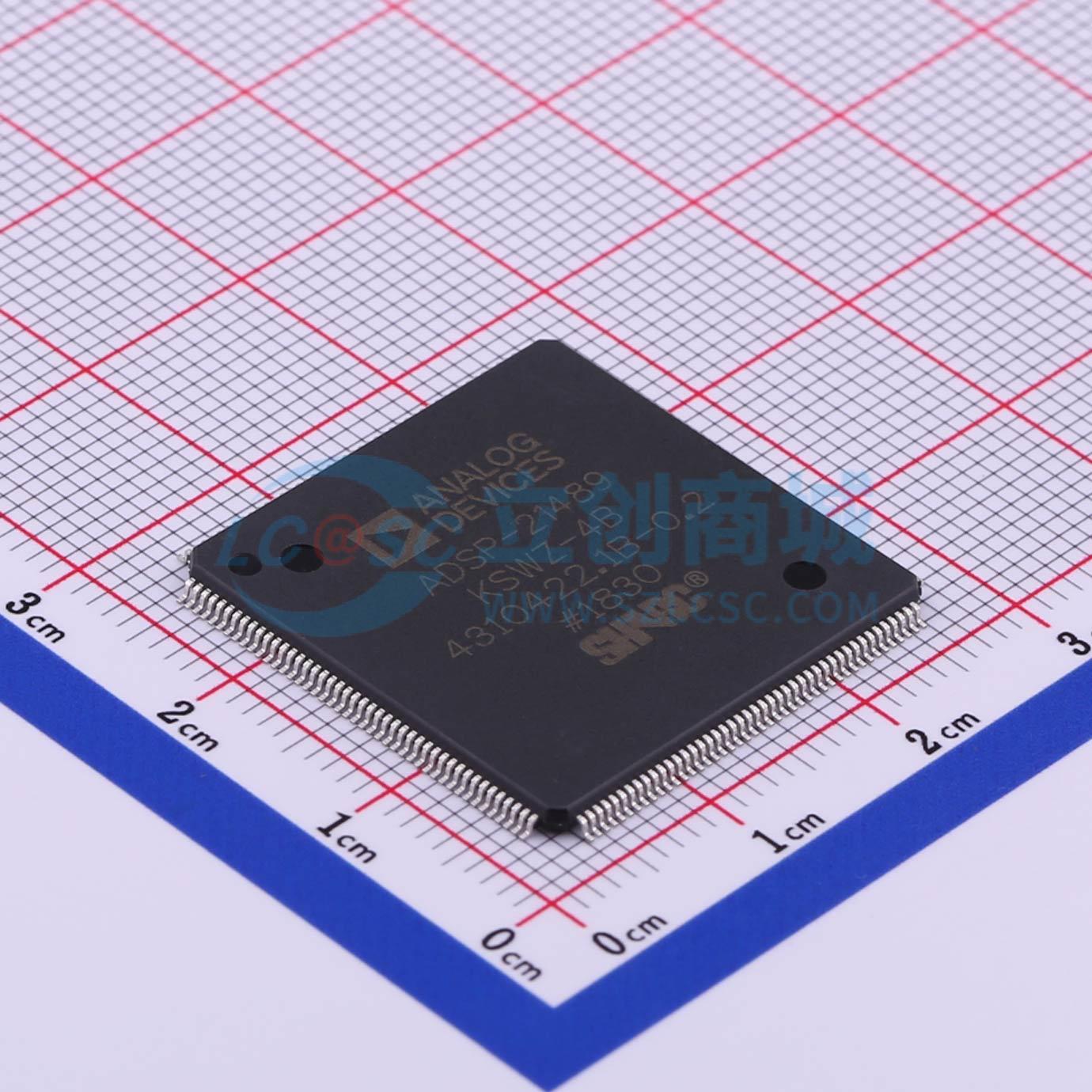

ADSP-21489KSWZ-4B

高性能32/40位浮点SHARC处理器

SMT扩展库PCB免费打样

私有库下单最高享92折

- 描述

- 高性能第四代DSP

- 品牌名称

- ADI(亚德诺)

- 商品型号

- ADSP-21489KSWZ-4B

- 商品编号

- C514365

- 商品封装

- LQFP-176-EP(24x24)

- 包装方式

- 托盘

- 商品毛重

- 1.86克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 数字信号处理器(DSP/DSC) | |

| 最大主频 | 400MHz | |

| FLASH容量 | - | |

| ROM容量 | 4MB |

| 属性 | 参数值 | |

|---|---|---|

| I/O数量 | - | |

| 工作温度 | 0℃~+70℃ | |

| 功能特性 | 硬件FFT加速;实时时钟与定时器;集成PWM控制;高速外设接口;循环缓冲支持;并行数据通道;DMA数据搬运;安全存储与保护;硬件乘加加速 |

商品概述

高性能32/40位浮点处理器,针对高性能音频处理进行优化 单指令、多数据(SIMD)计算架构 片内存储器:5 Mb片内RAM,4 Mb片内ROM 工作频率高达400 MHz 与SHARC系列的所有其它产品代码兼容 提供以音频中心的独特外设,例如:数字应用接口、串行端口、精密时钟发生器、S/PDIF收发器、异步采样速率转换器、输入数据端口等

ADSP-2148x SHARC处理器属于SIMD SHARC系列DSP,采用Super Harvard架构。该系列处理器与ADSP-2126x、ADSP-2136x、ADSP-2137x、ADSP-2146x、ADSP-2147x、ADSP-2116x DSP以及SISD(单指令、单数据)模式的第一代ADSP-2106x SHARC处理器源代码兼容。具有大容量片内SRAM,多条内部总线可消除I/O瓶颈,并且提供创新的数字应用接口(DAI)。

该系列处理器采样两个计算单元,相对于以前的SHARC处理器,其处理各种DSP算法的性能有了显著提高。利用SIMD计算硬件并以400 MHz速率运行时,该系列处理器能够执行2.4 GFLOPS。

商品特性

- 两个处理元件(PEx、PEy),各元件均由ALU、乘法器、移位器和数据寄存器文件组成

- 数据地址发生器(DAG1、DAG2)

- 带指令缓存的程序序列器

- PM和DM总线,支持存储器与内核之间在每个内核处理器周期传输2x64位数据

- 一个带引脚排列的周期性间隔定时器

- 片内SRAM (5 Mb)和屏蔽可编程ROM (4 Mb)

- 用于仿真和边界扫描的JTAG测试访问端口。JTAG通过用户断点提供软件调试功能,支持灵活的异常处理

- 用于32位数据传输的IOD0(外设DMA)和IOD1(外部端口DMA)总线

- 用于内核连接的外设和外部端口总线

- 带AMI和SDRAM控制器的外部端口

- 4个PWM控制单元

- 1个用于内部到内部存储器传输的存储器到存储器(MTM)单元

- 数字应用接口,包括4个精密时钟发生器(PCG)、1个用于串行和并行互连的输入数据端口(IDP/PDAP)、1个S/PDIF接收器/发送器器、4个异步采样速率转换器、8个串行端口和1个灵活的信号路由单元(DAI SRU)

- 数字外设接口,包括2个定时器、1个双线式接口(TWI)、1个UART、2个串行外设接口(SPI)、2个精密时钟发生器(PCG)、1个脉宽调制(PWM)单元和1个灵活的信号路由单元(DPI SRU2)

- 各处理元件内部有一组计算单元,由算术/逻辑单元(ALU)、乘法器和移位器组成,在单一周期中执行所有操作,并行排列,使计算吞吐速率达到最大

- 单一多功能指令执行并行ALU和乘法器操作,在SIMD模式下,并行ALU和乘法器操作同时在两个处理元件中进行

- 这些计算单元支持IEEE 32位单精度浮点、40位扩展精度浮点和32位定点数据格式

- 处理器包含一个内核定时器,用于产生周期性软件中断,可配置为利用FLAG3作为定时器到期信号

- 每个处理元件均包含一个通用数据寄存器文件,用于在计算单元与数据总线之间传输数据,以及存储即时结果

- 处理器的许多寄存器都有辅助寄存器,在中断处理期间可以将其激活以实现快速上下文切换

- USTAT (4)寄存器可以对所有外设寄存器(控制/状态)轻松进行位操作(置1、清0、反转、测试、XOR)

- 数据总线交换寄存器(PX)允许数据在64位PM数据总线与64位DM数据总线之间传送,或者在40位寄存器文件与PM/DM数据总线之间传送

- ADSP-2148x采用增强Harvard架构,利用独立的程序和数据存储器总线以及片内指令缓存,可在一个周期内同时获取4个操作数(每条数据总线2个)和1个指令

- 处理器含有一个片内指令缓存,支持三总线操作以获取一个指令和四个数据值,支持全速执行内核环路操作

- 两个数据地址发生器(DAG)用于间接寻址以及环形数据缓冲器的硬件实现,包含足够的寄存器,最多可以创建32个环形缓冲器,自动处理地址指针回绕

- 48位指令字支持各种并行操作,可实现简练编程

- 除了支持源自上一代SHARC处理器的标准48位指令以外,还支持新的16位和32位指令,此特性称为“可变指令集架构”(VISA)

- 程序序列器支持从内部和外部SDRAM存储器获取这些16位和32位指令

- 处理器的SRAM可以配置为最多160k字的32位数据、320k字的16位数据、106.7k字的48位指令(或40位数据)或不同大小字的组合,只要不超过5 Mb

- 所有存储器都可以通过16位、32位、48位或64位字访问,支持16位浮点存储格式,片内可存储的数据量得以加倍

- 32位浮点与16位浮点之间的转换通过单指令执行

- 使用DM总线和PM总线,一条总线专用于一个存储器模块,可保证单周期执行两个数据传输

其他推荐

- ADTL084ARUZ-REEL

- ADUM3223BRZ-RL7

- ADUM5401CRWZ-RL

- ADUM7440CRQZ-RL7

- ADUM7442CRQZ-RL7

- ADV212BBCZ-150

- ADV7123KSTZ50

- ADV7125JSTZ240

- ADV7125KSTZ50

- ADV7180BSTZ-REEL

- ADV7180WBCPZ-REEL

- ADV7181CWBSTZ-REEL

- ADV7181DBCPZ-RL

- ADV7280BCPZ-RL

- ADV7511KSTZ-P

- ADV7623BSTZ-RL

- ADV7842KBCZ-5

- ADV7842KBCZ-5P

- ADXL1001BCPZ

- ADXL203CE-REEL

- ADXL313WACPZ-RL