ATMEGA324PA-AU

Atmel picoPower ATmega324PA低功耗8位微控制器

- 描述

- ATmega324PA 是一款基于 AVR 增强 RISC 架构的低功耗 CMOS 8 位微控制器。通过在一个时钟周期内执行强大的指令,ATmega324PA 实现接近 1MIPS/MHz 的吞吐量。这使系统设计人员能够优化设备以实现功耗与处理速度之间的平衡。 AVR 核心结合了丰富的指令集和 32 个通用工作寄存器。所有 32 个寄存器都直接连接到算术逻辑单元 (ALU),允许在一个时钟周期内执行的单个指令访问两个独立的寄存器。由此产生的架构更有效地利用代码,同时实现比传统 CISC 微控制器快十倍的吞吐量。ATmega324PA 提供了以下特性:32K 字节的片内可编程 Flash,具有读写能力,1K 字节 EEPROM,2K 字节 SRAM,32 条通用 I/O 线,32 个通用工作寄存器,实时计数器 (RTC),三个具有比较模式和 PWM 的灵活定时/计数器,两个串行可编程 USART,一个面向字节的 2 线串行接口 (I2C),一个 8 通道 10 位 ADC,具有可选的差分输入级和可编程增益,一个具有内部振荡器的可编程看门狗定时器,一个 SPI 串行端口,符合 IEEE std. 1149.1 的 JTAG 测试接口,也用于访问片上调试系统和编程,以及六种软件可选的省电模式。空闲模式停止 CPU,同时允许 SRAM、定时/计数器、SPI 端口和中断系统继续运行。掉电模式保存寄存器内容,但冻结振荡器,禁用所有其他芯片功能,直到下一次中断或硬件复位。在省电模式下,异步定时器继续运行,允许用户在设备其余部分休眠时保持定时器基准。ADC 降噪模式停止 CPU 和所有 I/O 模块,除了异步定时器和 ADC,以最小化 ADC 转换期间的开关噪声。在待机模式下,晶体/谐振器振荡器正在运行,而设备其余部分正在休眠。这允许非常快的启动,同时结合低功耗。在扩展待机模式下,主振荡器和异步定时器都继续运行。

- 品牌名称

- MICROCHIP(美国微芯)

- 商品型号

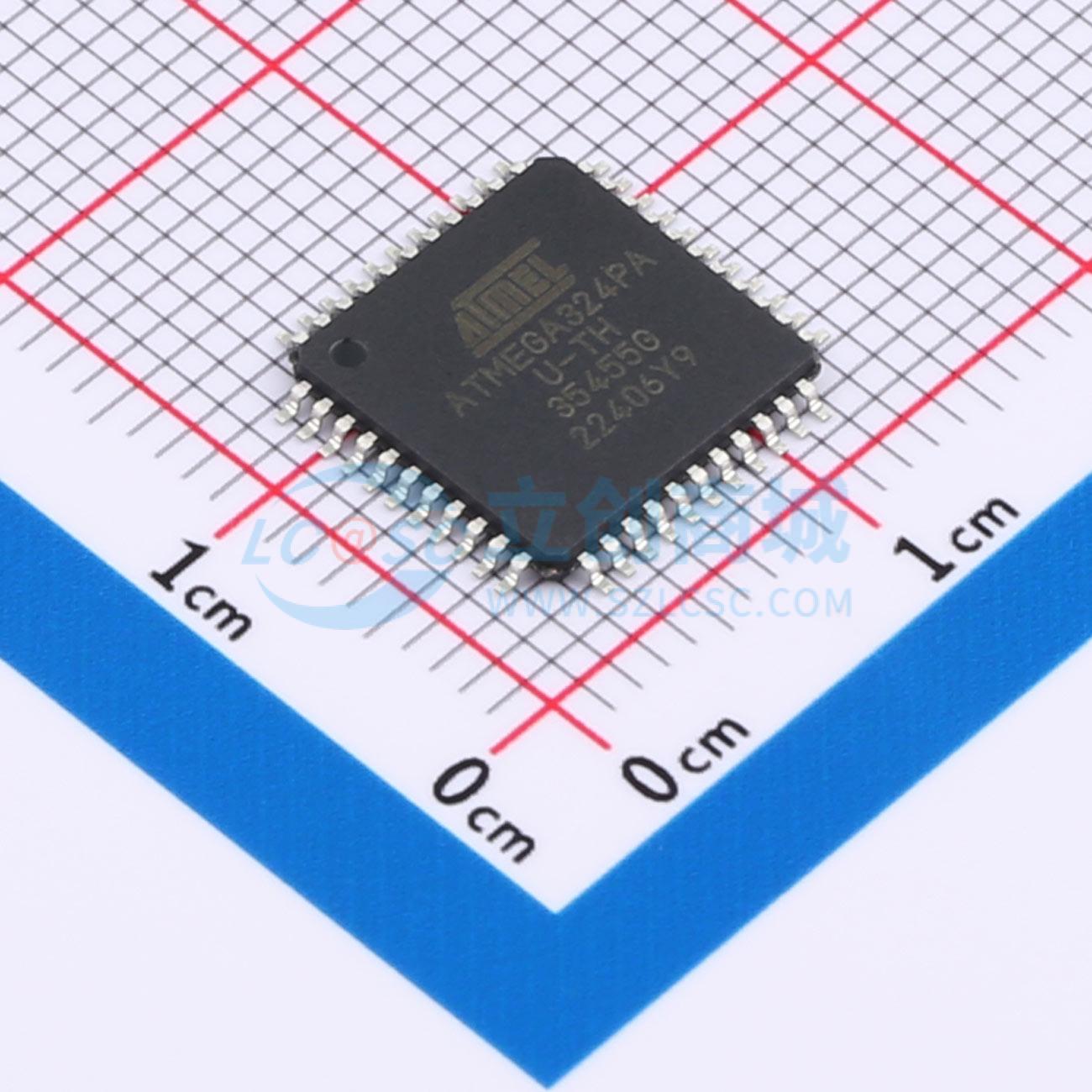

- ATMEGA324PA-AU

- 商品编号

- C47751

- 商品封装

- TQFP-44(10x10)

- 包装方式

- 托盘

- 商品毛重

- 1.499克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 单片机(MCU/MPU/SOC) | |

| CPU内核 | AVR | |

| CPU最大主频 | 20MHz | |

| CPU位数 | 8 Bit | |

| 程序存储容量 | 32KB | |

| 程序存储器类型 | FLASH | |

| RAM容量 | 2KB |

| 属性 | 参数值 | |

|---|---|---|

| EEPROM容量 | 1KB | |

| I/O数量 | 32 | |

| ADC(位数) | 10bit | |

| 振荡器类型 | 内置 | |

| 工作电压 | 1.8V~5.5V | |

| 工作温度 | -40℃~+85℃ | |

| 功能特性 | 欠压检测(BOR/LVD/LVR/LVI);上电复位(POR);看门狗复位;内置通用定时器;可编程看门狗;触控功能;外部管脚复位(NRST) |

商品概述

Atmel ATmega324PA 是一款基于 AVR 增强 RISC 架构的低功耗 CMOS 8 位微控制器。通过在一个时钟周期内执行强大的指令,ATmega324PA 实现接近 1MIPS/MHz 的吞吐量。这使系统设计人员能够优化设备以实现功耗与处理速度之间的平衡。

Atmel AVR 核心结合了丰富的指令集和 32 个通用工作寄存器。所有 32 个寄存器都直接连接到算术逻辑单元 (ALU),允许在一个时钟周期内执行的单个指令访问两个独立的寄存器。由此产生的架构更有效地利用代码,同时实现比传统 CISC 微控制器快十倍的吞吐量。

ATmega324PA 提供了以下特性:32K 字节的片内可编程 Flash,具有读写能力,1K 字节 EEPROM,2K 字节 SRAM,32 条通用 I/O 线,32 个通用工作寄存器,实时计数器 (RTC),三个具有比较模式和 PWM 的灵活定时/计数器,两个串行可编程 USART,一个面向字节的 2 线串行接口 (I2C),一个 8 通道 10 位 ADC,具有可选的差分输入级和可编程增益,一个具有内部振荡器的可编程看门狗定时器,一个 SPI 串行端口,符合 IEEE std. 1149.1 的 JTAG 测试接口,也用于访问片上调试系统和编程,以及六种软件可选的省电模式。空闲模式停止 CPU,同时允许 SRAM、定时/计数器、SPI 端口和中断系统继续运行。掉电模式保存寄存器内容,但冻结振荡器,禁用所有其他芯片功能,直到下一次中断或硬件复位。在省电模式下,异步定时器继续运行,允许用户在设备其余部分休眠时保持定时器基准。ADC 降噪模式停止 CPU 和所有 I/O 模块,除了异步定时器和 ADC,以最小化 ADC 转换期间的开关噪声。在待机模式下,晶体/谐振器振荡器正在运行,而设备其余部分正在休眠。这允许非常快的启动,同时结合低功耗。在扩展待机模式下,主振荡器和异步定时器都继续运行。