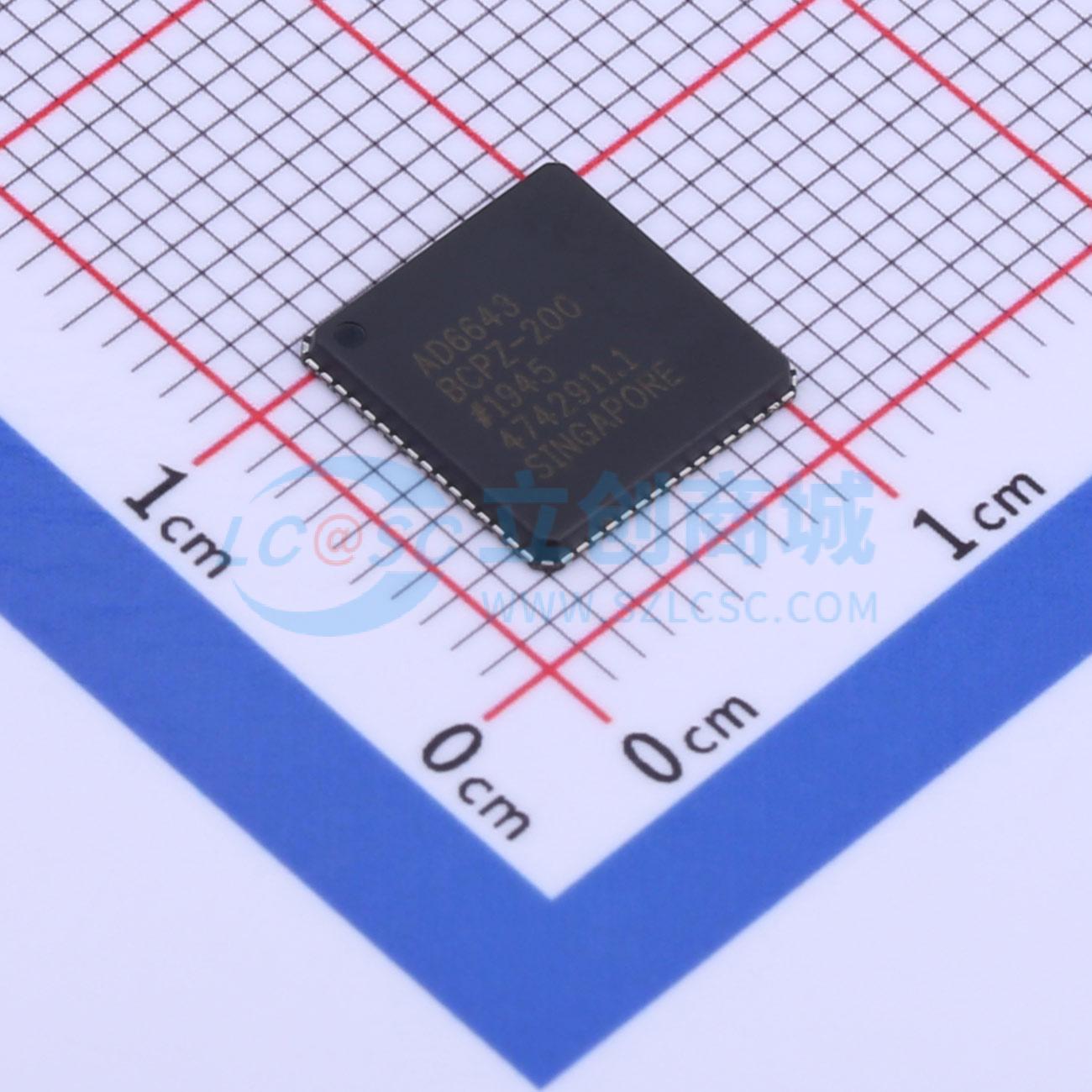

AD6643BCPZ-200

双通道中频接收机

- 品牌名称

- ADI(亚德诺)

- 商品型号

- AD6643BCPZ-200

- 商品编号

- C468505

- 商品封装

- LFCSP-64-EP(9x9)

- 包装方式

- 托盘

- 商品毛重

- 4.15克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 无线收发芯片 |

| 属性 | 参数值 | |

|---|---|---|

| 功能特性 | 支持软件复位 |

商品概述

AD6643是一款11位、200 MSPS/250 MSPS、双通道中频(IF)接收机,专门针对要求高动态范围性能、低功耗和小尺寸的电信应用中支持多天线系统而设计。 该器件包括两个高性能模数转换器(ADC)和噪声整形再量化器(NSR)数字模块。每个ADC由多级、差分流水线架构组成,并集成了输出纠错逻辑,每个ADC差分流水线的第一级包含一个宽带宽开关电容采样网络。集成基准电压源可简化设计。占空比稳定器(DCS)补偿ADC时钟占空比的波动,使转换器保持出色的性能。 各ADC的输出内部连接到NSR模块。集成NSR电路能够提高奈奎斯特带宽内较小频段的信噪比(SNR)性能。该器件支持两种不同的输出模式,通过SPI可以选择输出模式。如果使能NSR特性,则在处理ADC的输出时,AD6643可以在有限的部分奈奎斯特带宽内实现更高的SNR性能,同时保持11位输出分辨率。 可以对NSR模块进行编程,以提供采样时钟22%或33%的带宽。例如,当采样时钟速率为185 MSPS时,在22%模式下,AD6643可以在40 MHz带宽内实现最高75.5 dBFS的SNR;在33%模式下,它可以在60 MHz带宽内实现最高73.7 dBFS的SNR。 禁用NSR模块时,ADC数据直接以11位的分辨率提供给输出端。这种工作模式下,AD6643能够在整个奈奎斯特带宽内实现最高66.5 dBFS的SNR。因此,AD6643可以用于电信应用,例如要求更宽带宽的数字预失真观测路径。 经过数字信号处理后,多路复用输出数据路由至两个11位输出端口,最大数据速率为400 Mbps (DDR)。这些输出设置为LVDS,支持ANSI-644电平。 AD6643接收机能够对很宽的中频频谱进行数字化处理。各接收机设计用于同步接收不同的天线。该IF采样架构与传统的模拟技术或较低集成度的数字方法相比,能大幅度降低器件的成本和复杂度。 灵活的掉电选项可以明显降低功耗。器件设置与控制的编程利用三线式SPI兼容型串行接口来完成;该接口提供多种工作模式,支持电路板级系统测试。 AD6643采用64引脚无铅9 mm×9 mm脚架构芯片级封装(LFCSP_VQ),符合RoHS标准,额定温度范围为 -40°C至 +85°C工业温度范围。

商品特性

- 每个通道11位、250 MSPS输出数据速率

- NSR使能时的性能SNR:74.5 dBFS(55 MHz频段、90 MHz、250 MSPS时)SNR:72.0 dBFS(82 MHz频段、90 MHz、250 MSPS时)

- NSR禁用时的性能SNR:66.2 dBFS(90 MHz、250 MSPS时)SFDR:85 dBc(185 MHz、250 MSPS时)

- 总功耗:706 mW(200 MSPS)

- 1.8 V电源电压

- LVDS(ANSI-644电平)输出

- 1至8整数输入时钟分频器(最大输入频率625 MHz)

- ADC内部基准电压源

- 灵活的模拟输入范围1.4 V p-p至2.0 V p-p(标称值1.75 V p-p)

- 差分模拟输入、400 MHz带宽

- 95 dB通道隔离/串扰

- 串行端口控制

- 节能的掉电模式

- 小型、节省空间的9 mm×9 mm×0.85 mm、64引脚LFCSP封装集成两个ADC

- 引脚可选的噪声整形再量化器(NSR),当带宽降低至最大60 MHz、185 MSPS时,它能提高信噪比

- LVDS数字输出接口针对低成本FPGA系列而配置

- 采用1.8 V单电源供电

- 标准串行端口接口(SPI)支持各种产品特性和功能,例如:数据格式化(偏移二进制或二进制补码)、NSR、掉电、测试模式以及基准电压模式

- 片内1到8整数输入时钟分频器和多芯片同步功能支持广泛的时钟方案和多通道子系统

应用领域

- 通信

- 分集无线电和智能天线(MIMO)系统

- 多模式数字接收机(3G)WCDMA、LTE、CDMA2000WiMAX、TD-SCDMA

- I/Q解调系统

- 通用软件无线电