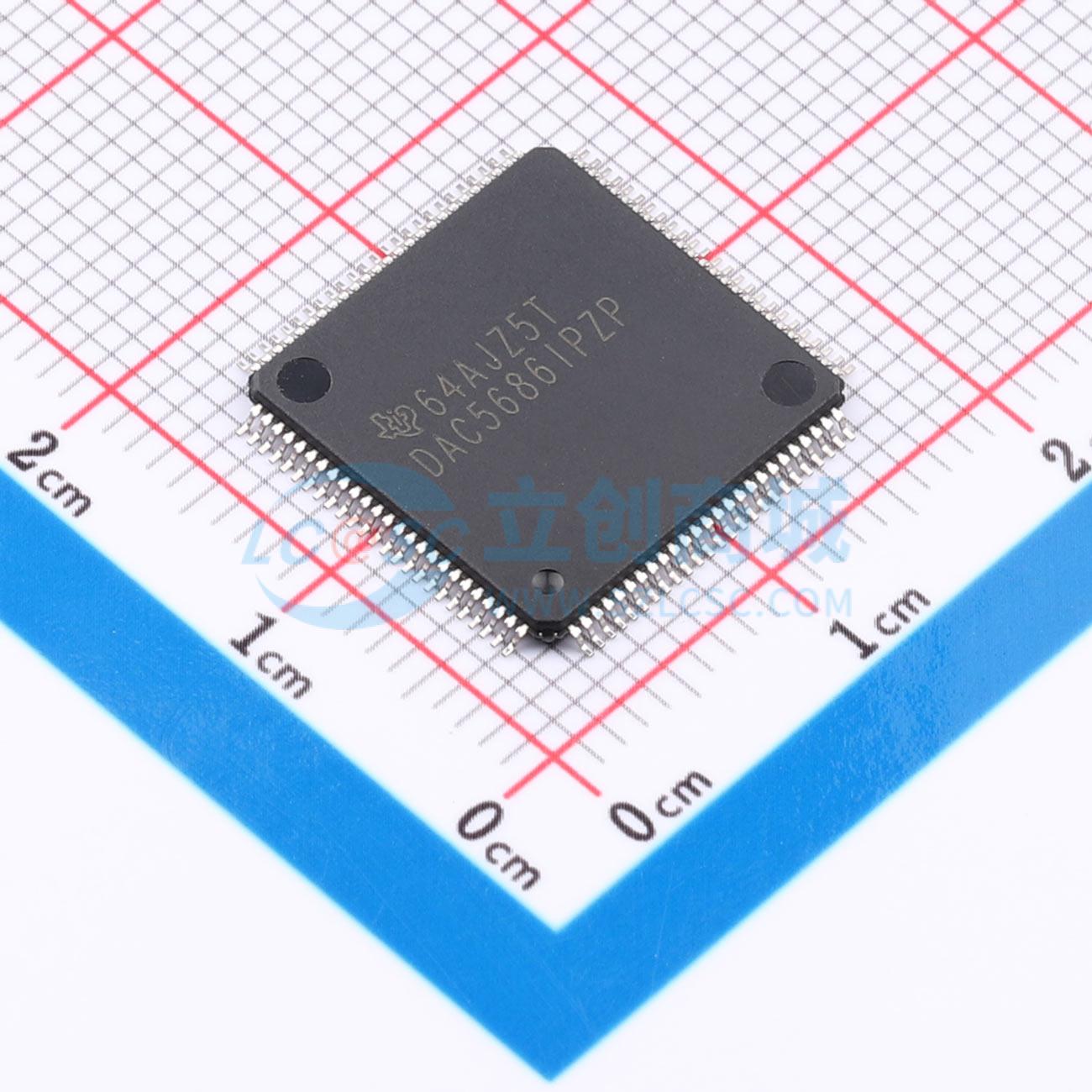

DAC5686IPZPG4

16位、500 Msps、2倍 - 16倍内插双通道数模转换器

- 描述

- 16位,500 MSPS,2x-16x插值双通道数模转换器

- 品牌名称

- TI(德州仪器)

- 商品型号

- DAC5686IPZPG4

- 商品编号

- C1555309

- 商品封装

- HTQFP-100(14x14)

- 包装方式

- 托盘

- 商品毛重

- 0.001克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | 数模转换芯片DAC | |

| 分辨率(位) | 16位 | |

| 通道数 | 2 | |

| 接口类型 | 并行 | |

| 工作电压 | 1.8V~3.6V | |

| 建立时间 | 12ns |

| 属性 | 参数值 | |

|---|---|---|

| 输出类型 | - | |

| 积分非线性 | 12LSB | |

| 工作温度 | -40℃~+85℃ | |

| 更新速率 | - | |

| 静态电流 | - |

商品概述

DAC5686是一款双通道16位高速数模转换器(DAC),集成了2倍、4倍、8倍和16倍插值滤波器、数控振荡器(NCO)、片上时钟乘法器和片上电压基准。DAC5686专门设计用于实现DAC与ASIC或FPGA之间的低输入数据速率,同时实现高输出发射中频(IF)。目标应用包括有线和无线通信系统中的高速数字数据传输以及高频直接数字合成(DDS)。 DAC5686提供三种工作模式:双通道模式、单边带模式和正交调制模式。在双通道模式下,插值滤波可提高DAC更新速率,从而减少sinx/x滚降,并允许使用要求较低的模拟后置滤波。 单边带模式为模拟正交调制器提供了另一种接口。通道载波选择在基带通过ASIC/FPGA中的混频来完成。来自ASIC/FPGA的基带I和Q信号输入到DAC5686,DAC5686进而进行复数混频,在其两个DAC的输出端产生希尔伯特变换对。然后,外部射频正交调制器进行最终的单边带向上变频。DAC5686的复数混频频率可通过32位可编程NCO灵活选择。 射频正交调制器的增益和偏移不匹配会导致不需要的边带和本振泄漏。DAC5686中的每个DAC都有11位偏移调整和12位增益调整功能,可补偿正交调制器的输入不平衡,从而降低射频滤波要求。 在正交调制模式下,片上混频实现基带至中频的向上变频。混频频率可通过32位可编程NCO灵活选择。通道载波选择在基带通过ASIC/FPGA中的复数混频来完成。来自ASIC/FPGA的基带I和Q信号输入到DAC5686,DAC5686将低数据速率信号插值到更高的数据速率。DAC5686的单DAC输出是呈现给射频的最终中频单边带频谱。 2倍、4倍、8倍和16倍插值滤波器采用半带2倍插值滤波器级联实现。对于插值率小于16倍的情况,未使用的滤波器会关闭以降低功耗。DAC5686提供全旁路模式,使用户能够绕过所有插值和混频功能。 DAC5686的PLL时钟乘法器控制数字滤波器和DAC内核的所有内部时钟。差分时钟输入和内部时钟电路可实现最佳抖动性能,支持正弦波时钟输入信号。PLL可由以DAC内核更新速率运行的外部时钟旁路。PLL的时钟分频器确保数字滤波器在正确的时钟频率下工作。 DAC5686的模拟电源电压为3.3 V,数字电源电压为1.8 V。数字I/O与1.8 V和3.3 V的CMOS兼容。在最大工作条件下,功耗为950 mW。DAC5686提供20 mA的标称满量程差分电流输出,支持单端和差分应用。输出电流可直接馈入负载,无需额外的外部输出缓冲器。该器件专门设计用于具有50 Ω双端接负载的差分变压器耦合输出。对于20 mA的满量程输出电流,支持4:1阻抗比(输出功率为4 dBm)和1:1阻抗比变压器(输出功率为 -2 dBm)。 DAC5686的工作模式通过串行接口对寄存器进行编程来配置。串行接口可配置为3引脚或4引脚接口,使其能够与许多行业标准的微处理器和微控制器进行通信。数据(I和Q)可以作为两个数据总线上的独立并行数据流输入到DAC5686,也可以作为一个数据总线上的单个交错数据流输入。 精确的片上1.2 V温度补偿带隙基准和控制放大器允许用户将满量程输出电流从20 mA调整到2 mA,提供20 dB的增益范围控制能力。或者,也可以应用外部基准电压以实现最大灵活性。该器件具有睡眠模式,可将待机功耗降低至约10 mW,从而最大限度地降低系统功耗。 DAC5686采用100引脚HTQFP封装。

商品特性

- 最高更新速率为500 MSPS的DAC

- WCDMA邻道功率比(ACPR):单载波,中频30.72 MHz时为76 dB,更新速率245.76 MSPS;单载波,中频61.44 MHz时为73 dB,更新速率245.76 MSPS;双载波,中频30.72 MHz时为72 dB,更新速率245.76 MSPS;四载波,中频92.16 MHz时为64 dB,更新速率491.52 MSPS

- 可选2倍、4倍、8倍和16倍插值

- 线性相位,通带纹波0.05 dB,阻带衰减80 dB,阻带过渡范围为0.4 - 0.6 fDATA

- 32位可编程NCO

- 带旁路模式的片上2 - 16倍PLL时钟乘法器

- 差分可缩放电流输出:2 mA至20 mA

- 片上1.2 V基准

- 1.8 V数字电源和3.3 V模拟电源

- 与1.8 V/3.3 V CMOS兼容的接口

- 最大工作条件下功耗为950 mW

- 封装:100引脚HTQFP

应用领域

- 蜂窝基站收发信机发射通道 – CDMA:W - CDMA、CDMA2000、IS - 95;TDMA:GSM、IS - 136、EDGE/UWC - 136

- 基带I和Q发射输入接口:用于与基带复数混频ASIC接口的正交调制

- 单边带向上变频

- 分集发射

- 电缆调制解调器终端系统