SN65LVDS108DBT

八通道LVDS中继器

SMT扩展库PCB免费打样

私有库下单最高享92折

- 描述

- SN65LVDS108 1:8 LVDS 时钟扇出缓冲器

- 品牌名称

- TI(德州仪器)

- 商品型号

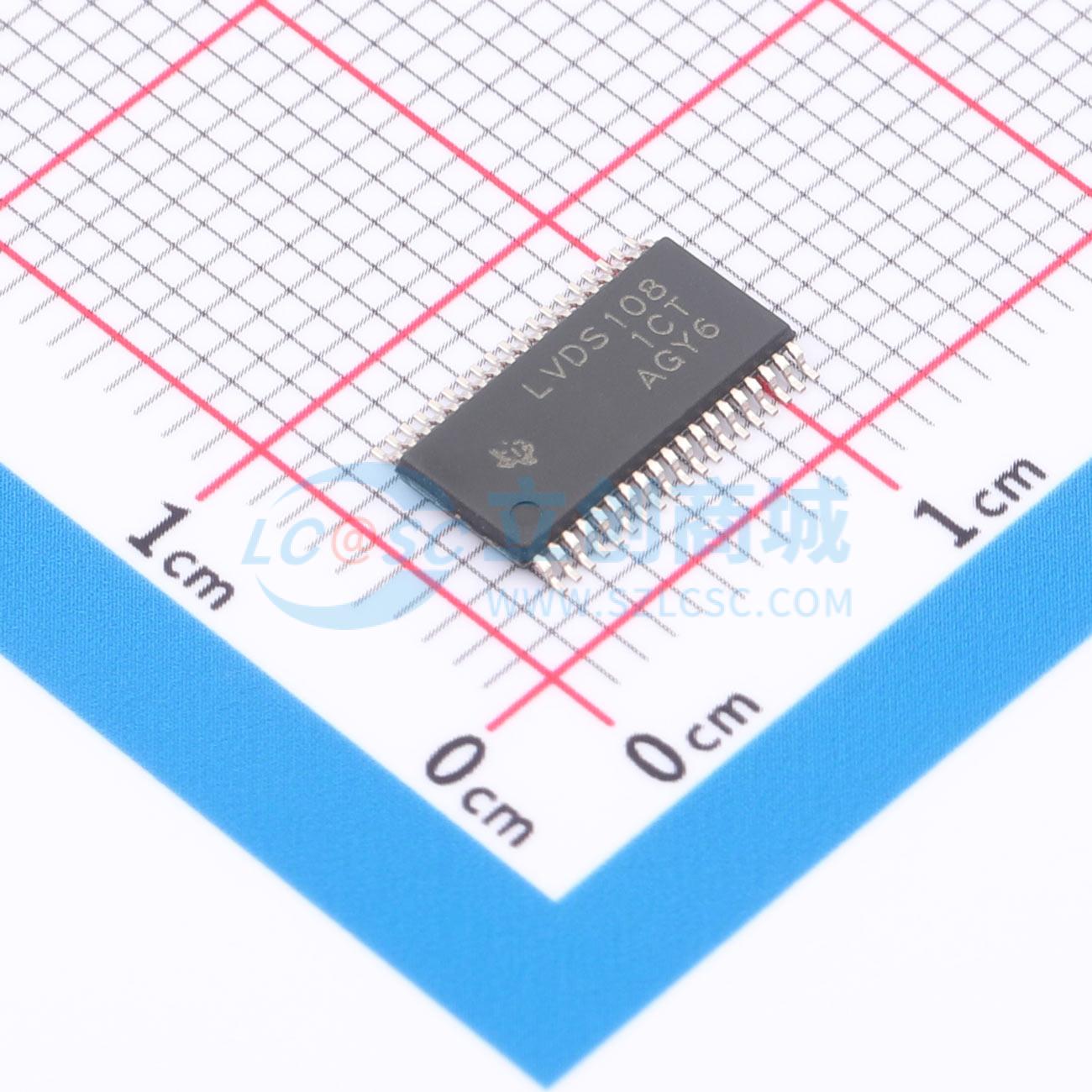

- SN65LVDS108DBT

- 商品编号

- C1527316

- 商品封装

- TSSOP-38-4.4mm

- 包装方式

- 管装

- 商品毛重

- 0.001克(g)

商品参数

| 属性 | 参数值 | |

|---|---|---|

| 商品目录 | LVDS芯片 | |

| 类型 | 中继器 | |

| 驱动器数 | 8 | |

| 接收器数 | 1 | |

| 工作电压 | 3V~3.6V |

| 属性 | 参数值 | |

|---|---|---|

| 数据速率 | 400Mbps | |

| 工作温度 | -40℃~+85℃ | |

| 电平标准 | LVDS | |

| 功能特性 | 故障安全 |

商品概述

SN65LVDS108配置为一个差分线路接收器连接八个差分线路驱动器。 每个输出都有独立的输出使能,并且所有输出还有一个额外的使能。 线路接收器和线路驱动器实现了低压差分信号(LVDS)的电气特性。如EIA/TIA - 644标准所规定,LVDS是一种数据信号技术,具有低功耗、低噪声辐射、高抗噪性和高开关速度的特点。 该器件及LVDS信号技术的预期应用是在约100Ω的受控阻抗介质上进行点对点或点对多点(分布式单工)基带数据传输。传输介质可以是印刷电路板走线、背板或电缆。集成在同一硅衬底上的大量驱动器,加上平衡信号的低脉冲偏斜,能使从输入重复的信号实现极其精确的时序对齐。这对于实现系统时钟或数据分配树特别有利。 SN65LVDS108的工作温度范围为 - 40℃至85℃。

商品特性

- 一个线路接收器和八个线路驱动器,配置为8端口LVDS中继器

- 线路接收器和线路驱动器满足或超过ANSI EIA/TIA - 644标准要求

- 典型数据信号速率达400 Mbps或时钟频率达400 MHz

- 使能逻辑允许对每个驱动器输出以及所有输出进行单独控制

- 低压差分信号,典型输出电压为350 mV,负载为100Ω

- 通过外部端接网络,与LVDS、PECL、LVPECL、LVTTL、LVCMOS、GTL、BTL、CTT、SSTL或HSTL输出电气兼容

- 传播延迟时间 < 4.7 ns

- 输出偏斜小于300 ps,器件间偏斜小于1.5 ns

- 200 MHz时,8通道使能情况下,总功耗典型值小于330 mW

- 禁用或VCC < 1.5 V时,驱动器输出或接收器输入呈高阻抗

- 总线引脚静电放电(ESD)保护超过12 kV

- 采用引脚间距为20密耳的薄型收缩小外形封装

相似推荐

其他推荐